Other Parts Discussed in Thread: TLV320AIC3254

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1180312/tlv320aic3254-startup-issue

器件型号:TLV320AIC3254我们正在尝试使 TLV320AIC3254编解码器在一对定制板上运行。 两个电路板都有一个 CC2652RSIPMOTR、该 CC2652RSIPMOTR 充当主器件并生成时钟线、并且使用 SimpleLink 音频插件(v3.30.006)。 一个板连接了麦克风、将发送 I2S 数据输出、另一个板将输入该数据并驱动线路电平输出。

[麦克风]--(模拟)->[TLV320A]--(I2S)->[CC2652]--(无线)->[CC2652]-[CC2652]-(I2S)->[TLV320A]--(模拟)->[线路输出]

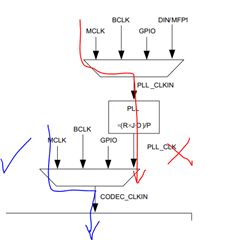

MCLK 为12MHz、使用示波器进行验证、当 CLKOUT 配置为将其路由到 GPIO (MFP5)时、也可以看到它。

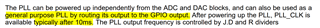

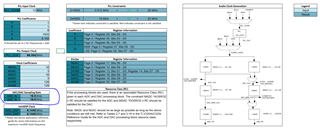

使用 AIC3254 CS 应用程序为16k 采样生成适当的 PLL_CLK 值;R 和 P 为1、J.D 为8.1920、M 为3、N 为16、AOSR 和 DOSR 为128。

这是使用以下值生成的 clockRegs 脚本:

{TI3254_PAGE_0、TI3254_CLK_MUX_REG、0x03}、 /* PLL 时钟为 CODE_CLKIN */

{TI3254_PAGE_0、TI3254_CLK_PLL_P_R_REG、0x80 | 0x11}、 /* PLL 上电、P=1、R=1 */

{TI3254_PAGE_0、TI3254_CLK_PLL_J_REG、0x08}、 /* J=8 */

{TI3254_PAGE_0、TI3254_CLK_PLL_D_MSB_REG、0x07}、 /* D = 0780 */

{TI3254_PAGE_0、TI3254_CLK_PLL_D_LSB_REG、0x80}、 /* D = 0780 */

{TI3254_PAGE_0、TI3254_CLK_NDAC_REG、0x80 | 0x10}、 /* NDAC 分压器加电、NDAC = 16 */

{TI3254_PAGE_0、TI3254_CLK_MDAC_REG、0x80 | 0x03}、 /* MDAC 分压器加电、MDAC = 3 */

{TI3254_PAGE_0、TI3254_DAC_OSR_MSB_REG、0x00}、 /* DOSR = 0x0080 = 128 */

{TI3254_PAGE_0、TI3254_DAC_OSR_LSB_REG、0x80}、 /* DOSR = 0x0080 = 128 */

{TI3254_PAGE_0、TI3254_CLK_NADC_REG、0x80 | 0x10}、 /* NADC 分压器通电、NADC = 16 */

{TI3254_PAGE_0、TI3254_CLK_mAdc_REG、0x80 | 0x03}、 /* mAdc 分频器通电、mAdc = 3 */

{TI3254_PAGE_0、TI3254_ADC_OSR_REG、0x80}、 /* AOSR = 128 ((与 PRB_R1配合使用至 PRB_R6、ADC 滤波器类型 A)*

添加以下内容:

{TI3254_PAGE_0、0x34、0x10}、

{TI3254_PAGE_0、0x1A、0x80 | 0x64}、

{TI3254_PAGE_0、0x19、0x03}、

用于设置 CDIV_CLKIN、CLKOUT M 和 MPF5 GPIO。

但 GPIO 仅保持其高电平状态。 如果最后一个寄存器0x19更改为0x00值以显示 MCLK、那么我们将得到一个120kHz 的时钟、正如预期的那样。