Other Parts Discussed in Thread: PCM1840

您好!

我们在 PCM1840中对板进行了设计。 有5个 ADC、1个作为主器件、4个作为从器件。 经过几次调整后、这些功能效果良好、FPGA 中的处理功能也非常好。

我们现在的问题是以下序列是否正常、或者是否仍需要调整才能实现稳定运行。

INFO:AVDD = IOVDD、电压电平相同、为3、3V

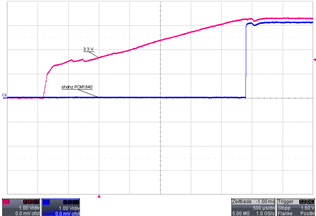

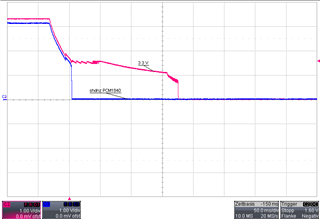

1.上电行为:

数据表中的信息:3.3V 电源稳定后、Shdnz 必须保持100us 低电平。

但是、3.3V 被视为稳定的电压电平是多少?

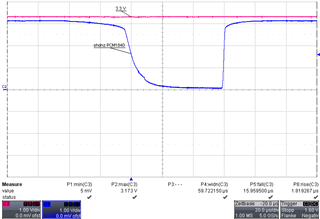

2.正常运行期间的复位(AVDD 和 IOVDD 在3、3V 电压电平下保持稳定):

我们在数据表中未找到活动复位的最短时间(shdnz =低电平)。 这段时间是否足以复位 ADC、或者在 shdnz 上复位 ADC 的最短时间是多少?

3.断电:

如果电源出现故障、我们 无法 将关断引脚(SHDNZ)拉至低电平(关断有效) 10ms 或 AVDD 和 IOVDD 在最小建议电压3.0V 下下降之前的任何时间

当该电压下降时、ADC 数据不再被处理。 这意味着 ADC 在其数据线路上提供什么都无关紧要。

在这个序列之后、它会像在"1. 上电行为"

这种行为是否正常?

我们现在的问题是、序列1、2和3是否正常、或者我们的客户是否仍需要调整才能在现场稳定运行?

我们期待您提供更多信息反馈。

谢谢、最诚挚的谢意、