在我们的应用中、我们使用 TLV320ADC3140作为4通道 ADC、目前只有第三个通道有模拟输入。 在 ASI 输出中,有时第三 时隙的数据会漂移到第二时隙或第四时隙。如何解决它?

- 下面列出了主要特性点。

- AREG 是使用片上稳压器生成的。

- TLV320ADC3140配置 为音频总线主器件。

- ASI 输出32个通道、具有 16位数据宽度。

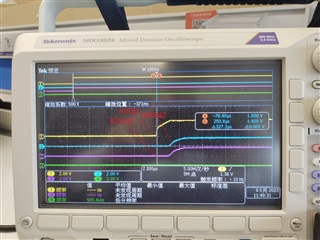

第一幅图 显示了正确的第三时隙中的输出 PCM 数据。

第二幅图显示输出 PCM 数据漂移到第四个时隙。

寄存器配置:

静态空 adcx140_enable (结构 adcx140_priv *adcx140)

{

regmap_write (adcx140->regmap、0x01、0x01);//μ 复位

usleep_range (10000、100000);

regmap_write (adcx140->regmap、0x02、0x81);//μ 退出sleep

usleep_range (10000、100000);

regmap_write (adcx140->regmap、0x07、0x03);//μ ASI配置

regmap_write (adcx140->regmap、0x08、0xa1);// ASI配置

regmap_write (adcx140->regmap、0x0B、0x00);//μ 通道顺序配置

regmap_write (adcx140->regmap、0x0c、0x01);

regmap_write (adcx140->regmap、0x0d、0x02);

regmap_write (adcx140->regmap、0x0E、0x03);

regmap_write (adcx140->regmap、0x0F、0x04);

regmap_write (adcx140->regmap、0x10、0x05);

regmap_write (adcx140->regmap、0x11、0x06);

regmap_write (adcx140->regmap、0x12、0x07);

regmap_write (adcx140->regmap、0x6c、0x20);//dsp、1biquad 每个通道

regmap_write (adcx140->regmap、0x21、0xa0);//μ 选择MCLK

regmap_write (adcx140->regmap、0x14、0x4a);//48K,16*μ 32通道

regmap_write (adcx140->regmap、0x13、0x81);//master,PLL enable

regmap_write (adcx140->regmap、0x16、0x08);//μ MCLK和WS的倍数

regmap_write (adcx140->regmap、0x3c、0x20);// CH1单端模拟输入

regmap_write (adcx140->regmap、0x41、0x20);// CH2单端模拟输入

regmap_write (adcx140->regmap、0x46、0x20);//μ CH3单端模拟输入

regmap_write (adcx140->regmap、0x4b、0x20);//μ CH4单端模拟输入

regmap_write (adcx140->regmap、0x22、0x00);//μ 关闭GPO0

regmap_write (adcx140->regmap、0x23、0x00);//μ 关闭GPO1

regmap_write (adcx140->regmap、0x24、0x00);//μ 关闭GPO2

regmap_write (adcx140->regmap、0x25、0x00);//μ 关闭GPO3

regmap_write (adcx140->regmap、0x2b、0x00);//关闭GPI0 1.

regmap_write (adcx140->regmap、0x2C、0x00);//关闭GPI2 3.

regmap_write (adcx140->regmap、0x73、0xf0);//μ 使能输入通道

regmap_write (adcx140->regmap、0x74、0xf0);// ASI使能输出

regmap_write (adcx140->regmap、0x75、0x60);//使能ADC、使能PLL

}