嗨、团队,

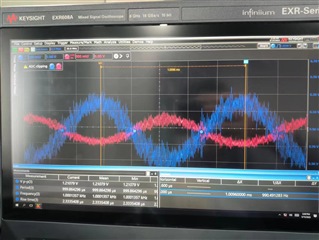

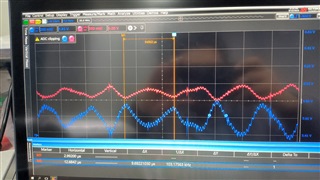

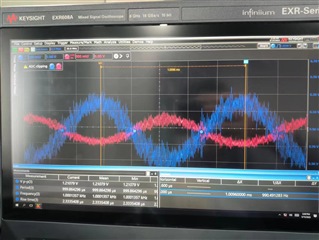

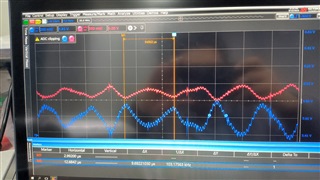

对于 TDM、当客户播放1kHz 音频时、他发现输出波形上叠加了100kHz 左右的杂波。 此时、故障是音频正在播放、而音频未在播放。 我希望 BU 可帮助了解该信号是否与 DSP 或功率放大器6424L 相关?

输出:红色和蓝色

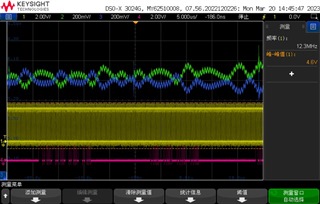

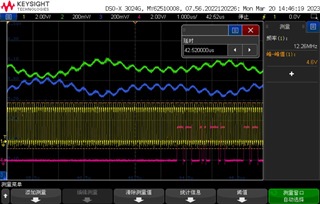

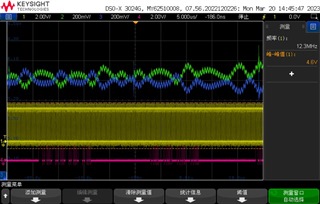

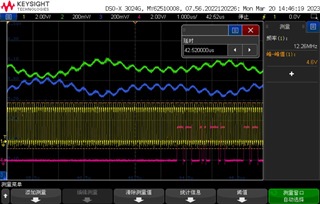

SCLK:黄色

SDIN:粉红色

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、团队,

对于 TDM、当客户播放1kHz 音频时、他发现输出波形上叠加了100kHz 左右的杂波。 此时、故障是音频正在播放、而音频未在播放。 我希望 BU 可帮助了解该信号是否与 DSP 或功率放大器6424L 相关?

输出:红色和蓝色

SCLK:黄色

SDIN:粉红色

尊敬的 Gregg:

在今天对客户进行初步故障排除和测试后、我附上了当前的测试报告和原理图、希望帮助我分析可能出现的问题。 从我目前的角度来看、寄存器配置似乎没有明显的问题。 希望您可以帮助我访问 look.e2e.ti.com/.../SD3A-Main-Board_5F00_V1.1_5F00_20230321_2D002D00_AMP.pdfe2e.ti.com/.../Analysis-of-Excessive-Audio-Background-Noise-in-TAS6424_2D002D00_20230321-.docx

Hy Shadow,

客户反馈 PVDD 的波形相对稳定。

4 Ω 电阻是指原理图中对应位置的电阻。

我希望 BU 可以帮助查看客户的布局图。 附加的是客户版式的文件。

e2e.ti.com/.../_CC53_E04_7998EE76_TAS6424_2600_TAS6422-Layout_08FF_8_425C7F6709FF_.zip