https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1207951/pcm1863-timing-requirements

器件型号:PCM1863您好!

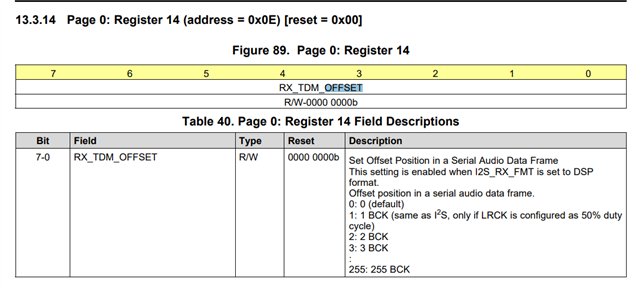

中、将"时序要求"部分增加到"6.25"。

(1) tBCKL 最小值为1.5 x tSCKI。

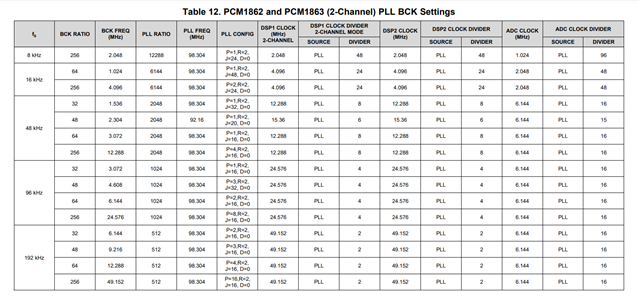

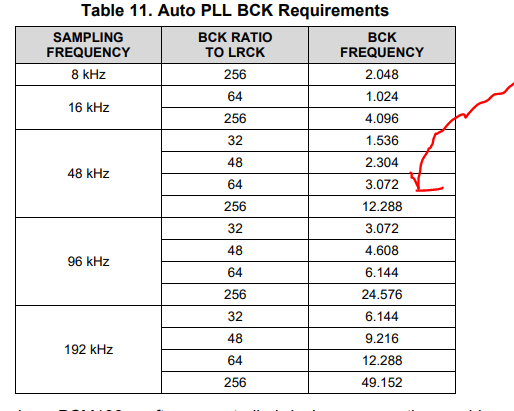

在我们的客户使用的是具有 PLL bck 输入的 I2S 从模式。

在这种情况下、不使用 SCKI、但内部 PLL 会生成 SCK。

我们是否应该将您的要求转换为1.5 x tSCK?

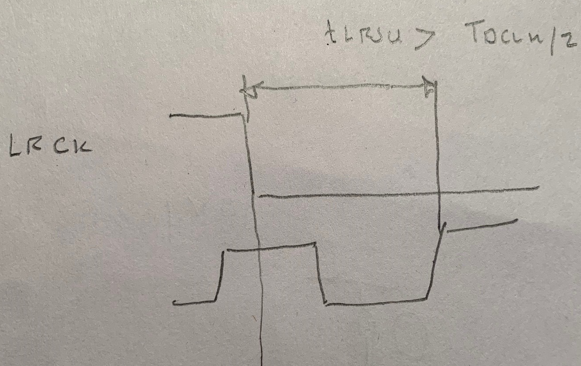

(2) tLRSU 最小值为50ns。

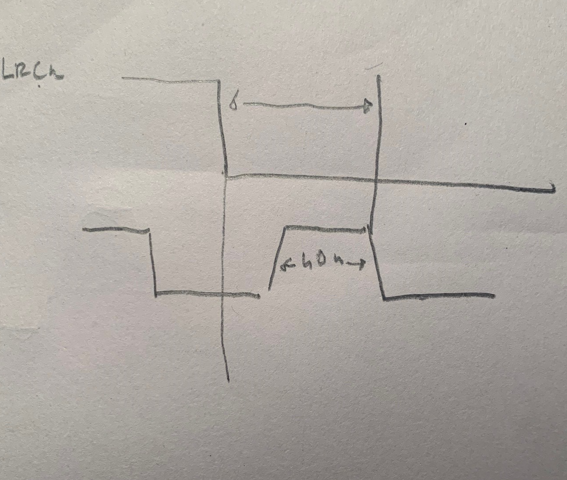

在192KHz 采样数据时、LRCK 周期为81.4ns、建立时间变为40.7ns。

我们无法满足 tLRSU 要求、这种差异的原因是什么。

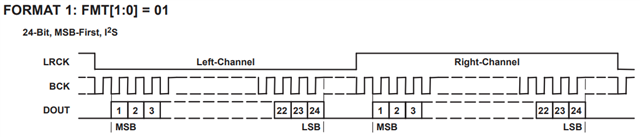

(3) tLRDO =-10 ~ 40ns

在 Fs48KHz 64BCK 条件下、器件输出 tLRDO 的实际捕获值为320ns。

这种差异的原因是什么?

(4) tLRHD 阈值 LRCK 为1.4V、BCK 为1.4V

但绘制的 LRCK 阈值看起来为90%、哪一项正确?

此致、

Mochizuki