请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TAS6424E-Q1 如何理解 TSF 和 TFS、请举个例子、谢谢!

请您为这些参数提供一个实际示例(波形上的实际点是什么),谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

如何理解 TSF 和 TFS、请举个例子、谢谢!

请您为这些参数提供一个实际示例(波形上的实际点是什么),谢谢!

你好、刘健

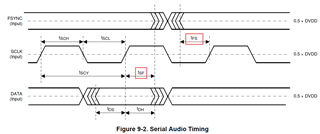

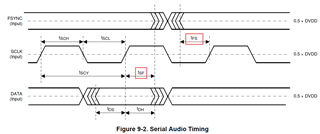

LRCLK"意思是"FSYNC"?

是的、FSYNC 和 LRCLK 是相同的、它的名称与不同文献不同。

FSYNC"级别更改(低-->高或高-->低)应该在 的点 发生 对吧? [/报价]是的、这是使用的标准。

[/quote]如何理解8ns? [/报价]这是数字侧用于保证时钟安全的最短时间。 上升沿是 SCLK 的有效点、当 FSYNC 需要变化时、翻转位置需要远离 SCLK 的上升沿。