Other Parts Discussed in Thread: PCM3168A

主题中讨论的其他器件: PCM3168

尊敬的

PCM3168A 配置为 TDM8输出、并结合 LRCKAD 和 LRCKDA 来连接主控制芯片的 LRCK

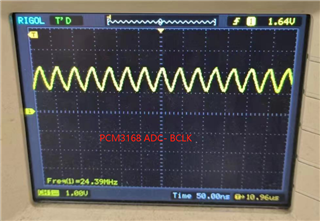

BCKAD 和 BCKDA 合并后、BCKAD 连接到主控制芯片的 bck=12.288M、主控制的 SPI 模式、PCM3168作为从器件、采样率 LRCK:48K MCLK:12.88M、bck:12.288M;

Addr=42、val=0

Addr=43、val=0

Addr=44、val=0

Addr=45、val=0

Addr=46、val=0

Addr=47、val=ff

Addr=48、val=ff

addr=49、val=ff

Addr=4a、val=ff

Addr=4b、val=ff

Addr=4c、val=ff

Addr=4d、val=ff

Addr=4e、val=ff

Addr=4F、val=ff

addr=50、val=1

addr=51、val=6

addr=52、val=0

addr=53、val=0

Addr=54、val=0

Addr=55、val=0

Addr=56、val=0

Addr=57、val=0

addr=58、val=D7

addr=59、val=D7

addr=5a、val=D7

Addr=5b、val=D7

Addr=5c、val=D7

Addr=5d、val=D7

Addr=5e、val=D7

--readback--:

addr=c0、val=c0

addr=c1、val=6

Addr=C2、val=0

Addr=C3、val=0

addr=c4、val=0

Addr=C5、val=ff

Addr=C6、val=0

Addr=C7、val=ff

Addr=C8、val=ff

Addr=C9、val=ff

Addr=ca、val=ff

Addr=cb、val=ff

Addr=cc、val=ff

Addr=cd、val=ff

Addr=ce、val=ff

Addr=cf、val=ff

addr=d0、val=1

addr=D1、val=6

Addr=D2、val=0

Addr=D3、val=0

Addr=D4、val=0

Addr=D5、val=0

addr=d6、val=0

Addr=D7、val=0

Addr=D8、val=D7

Addr=D9、val=D7

addr=da、val=d7

Addr=db、val=D7

addr=dc、val=d7

Addr=dd、val=d7

addr=de、val=D7

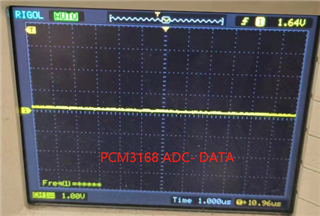

TDM8 48K 从机模式的输出正常。 采样率达到96k 后、单速率、双速率、自动速率的输出异常。 请帮助检查需要更改的96K 的配置、谢谢! 当配置为双速率或自动模式时、ADC 数据不会生成波形;当配置为单速率时、会出现噪声

您好, Andrew 它 是 100MHz

您好, Andrew 它 是 100MHz