Other Parts Discussed in Thread: PCM1861

作为 I2S 从设备运行的 PCM1861遇到问题。 在我们产品的某个工作模式下、我们的主微控制器(I2S 主器件) 将重复短暂地停止 I2S 时钟。 发生这种情况时、我观察到输入信号线路短暂地低于接地值(约1ms)。 如果其它器件连接到同一条输入线路、则会听到不可取的爆裂噪音。

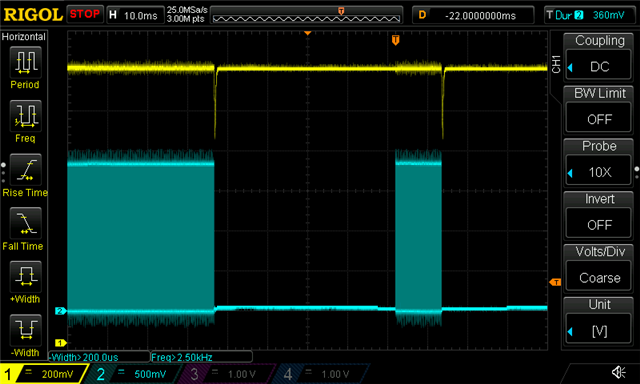

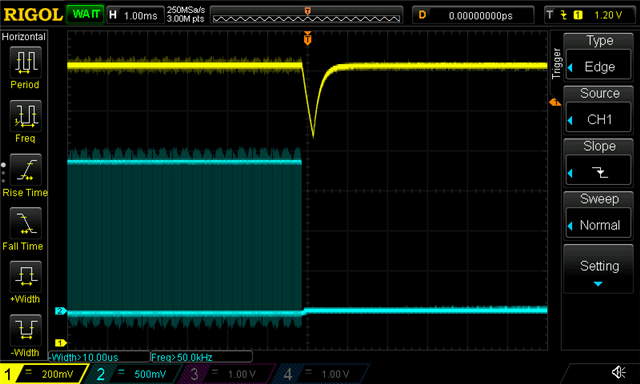

在下面的屏幕截图中、上面的迹线是音频输入信号线(直接在 PCM1861输入上)、下面的迹线是来自微控制器的 I2S LRCK。 可以看到、输入开始线性下降、然后在 I2S 时钟暂停后立即以对数方式上升。 BCK 时钟也同时停止。

所有配置引脚均被拉至零(直接接地)。 请参阅下面的原理图:

我们使用2个声道作为单端音频源。 它们的连接方式与数据表中完全相同、具有附加的抗混叠滤波器、并且增加了一个100k 电阻接地、我认为这可能是多余的:

作为参考、这是 PCM186x 数据表的输入原理图:

如果没有任何设备连接到音频输入、也会观察到下降。 因此、电流骤降/干扰必须由 PCM1861引起。

什么导致输入下降? 我们是否可以对此采取某些措施? 我们无法完全控制 I2S 时钟信号、因此无法确保其同时保持运行。

提前感谢您的帮助。