主题中讨论的其他器件: TAS5411Q1EVM

您好、支持团队

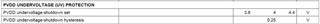

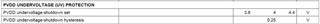

我们测试 PVDD 为13v 并且压降为4.2V、这可以触发"PVDD 欠压故障寄存器"、但如果 PVDD 为5V 压降为4V、则无法触发"PVDD 欠压故障寄存器"。

IC 行为是否正常?

注意:压降阶跃为0.1V

如有任何建议、请告知我。

谢谢。

此致、

劳伦斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、支持团队

我们测试 PVDD 为13v 并且压降为4.2V、这可以触发"PVDD 欠压故障寄存器"、但如果 PVDD 为5V 压降为4V、则无法触发"PVDD 欠压故障寄存器"。

IC 行为是否正常?

注意:压降阶跃为0.1V

如有任何建议、请告知我。

谢谢。

此致、

劳伦斯

高阴影:

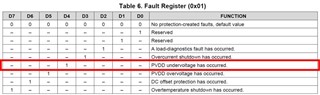

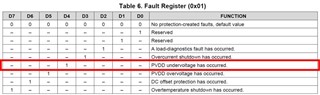

我的客户已使用 EVM 且其系统板将 PVDD(Vin)从5V 调节,然后突然直接降至4V,TAS5411-Q1无法触发 PVDD UVLO 故障。 我请求客户获取两个寄存器0x01并获取 PVDD/故障波形、您可以看到以下日志0x01将不会触发 PVDD UVLO (0x01 = 0x00)、但很奇怪为什么故障会触发低电平~ 1.16秒、然后恢复到正常高电平。 客户想知道

(1). 为什么每次以0.1V 的间隔缓慢地将 PVDD 调整为4.2V ,TAS5411-Q1可以触发 PVDD UVLO 是没有问题的, 但如果 从5V 调节 PVDD (Vin),然后突然降至4V, UVLO 不会触发 ?

(2). TAS5411-Q1内部 PVDD UVLO 触发行为是什么 ? 谢谢!

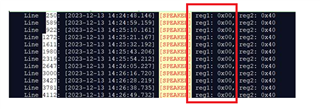

->测试日志寄存器0x01 = 0x00 。当 PVDD (Vin)从5V 突然下降到4V 时

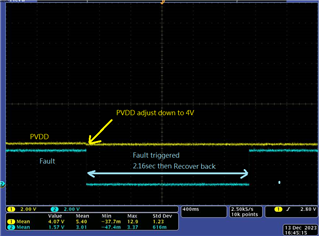

-> PVDD 和故障波形(PVDD 测量点:关闭 IC 引脚15电容器点),可以看到以下波形故障触发2.16秒 ,然后恢复到正常当 PVDD(Vin)从5V 调整,然后突然下降到4V 直接

你好,罗伊

对于该功能、内部电路非常清楚。 使用比较器报告此故障。 比较器的一侧来自 PVDD 并由电阻器分压。 比较器的另一侧来自内部 LDO 输出、用于设置基准。 突然下降应该没有问题触发。

最后一张图片、它仍然是非常低的压降、对吧? PVDD 的压降似乎很小、可能仅为0.1V。 2.16s 后、FAULT 引脚恢复、此时 PVDD 值可能仍非常接近阈值、仍可能报告为正常。

我们是否能够捕获5V 波形的突然下降? 我不知道目前如何产生该压降、电路板上应该有 PVDD 电容器、电容器是否可能保持电压、是否需要一些时间才能完全压降?

劳伦斯·海

同时我们的客户测试 TAS5411Q1EVM ,如果移除 U2 IC , PVDD 电源来自直流电源,[/报价]那么、我们为 EVM 提供外部3.3V 电源、对吧? 实际上、对于 PVDD 降至4V 测试、可能无需这样做。 可以直接测试 EVM。

[/quote]我们会发现欠压问题。

TAS5411EVM:

[/报价]对于您要显示的结果、我有一点困惑。 波形图似乎显示 PVDD 降至4V、而 FAULT 引脚拉至低电平、这是正确的行为。 寄存器0x01也读取值0x10、表示检测 PVDD 欠压。 请问我们所讨论的问题是什么?