Other Parts Discussed in Thread: TLV320ADC3100, TLV320ADC3120

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1301482/tlv320adc3100-tlv320adc3100

器件型号:TLV320ADC3100主题中讨论的其他器件: TLV320ADC3120

您好!

我们正在将 TLV320ADC3100音频编解码器 用于我们的项目。 我们首先写入寄存器、然后通过读取寄存器对其进行验证。 不过、我们 在读取该寄存器后获得的值与我们在该寄存器中写入的值不同。 对于 I2C 外设、我们有没有需要注意的东西?

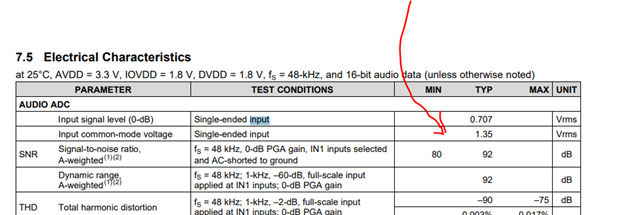

我们已将音频编解码器配置为主模式、并且所需的输出为:

BCLK:2.8224Mhz

WCLK:44.1kHz

样本大小:32位

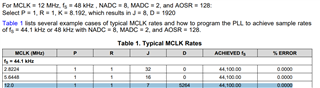

我们给出的 MCLK 为12.288Mhz。

此外、下面是配置的寄存器的值。

ADC310X_PAGE_SELECT - 0x00 //页-选择0

ADC310X_RESET - 0x01 //软复位

ADC310X_CLK_GEN_MUX - 0x00 //时钟生成

ADC310X_PLL_PR_VAL - 0x91 // PLL_CLK - 90.3168

ADC310X_PLL_J_VAL - 0x07 // J - 7

ADC310X_PLL_D_VAL_MSB - 0x0D //

ADC310X_PLL_D_VAL_LSB - 0xAC //对于 D,MSB 和 LSB 的组合是3500

ADC310X_NADC_CLK - 0x88 // NADC - 8

ADC310X_mAdc_CLK - 0x82 // mAdc - 2、根据我们的计算

ADC310X_AOSR - 0x80 //过采样- 128

ADC310X_ADC_IADC - 0x20 // IADC - 32

ADC310X_ADC_INTF_CTRL_1 - 0x3C //适用于具有32位样本大小的 ADC 接口的 I2S、BCLK 和 WCLK 都作为输出

ADC310X_ADC_INTF_CTRL_2 - 0x06 // BDIV_CLKIN = ADC_CLK、即使编解码器断电、也都处于活动状态

ADC310X_BLCK_N_DIV - 0x82 //值为2、如我们的计算结果所示。

ADC310X_ADC_PROC_BLK- 0x01 // ADC 信号处理块 PRB_R1

ADC310X_PAGE_SELECT - 0x01 // 页-选择1

ADC310X_PGA_ANALOG_L - 0x00 // 左 PGA 增益= 0dB 并静音

ADC310X_PGA_ANALOG_R - 0x00 // 右侧 PGA 增益= 0dB 并静音

ADC310X_INPUT_SEL_PGA_L_1 - 0xFC // 左侧 PGA 的左侧 ADC 输入选择= IN1L (P)为单端

ADC310X_INPUT_SEL_PGA_R_1 - 0xFC // 右侧 PGA 的右侧 ADC 输入选择= IN1R (M)为单端

ADC310X_PAGE_SELECT - 0x00 页- 2 选择。

ADC310X_ADC_DIGITAL - 0xC2 // 为左侧 ADC 和右侧 ADC 上电

ADC310X_ADC_VOL_CTRL - 0x00 //解除数字音量控制静音并设置增益= 0dB

请提供一些建议。

谢谢、此致

莱克希塔

。

。