请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPA3255

尊敬的团队:

IC TPA3255 在故障状态下始终具有低逻辑电平、

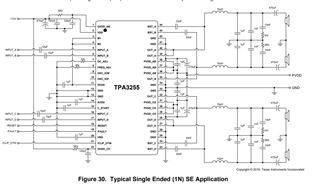

它在 SE 模式下工作、PVDD =36V、GVDD =12V

为 OUT_A 和 OUT_B 连接负载4R、工作功率仅为10W、音量为100%、然后故障引脚始终= 0

检查后、我注意到 AVDD 引脚= 0V 并非通常为7.7V。 因此、此 SE 模式无法在4R 负载下工作?