您好、支持团队

我们看过应用报告:《 具有共享 TDM 和 I2C 总线的 SBAA415多个 PCm6xx0器件》

我们有2个问题、如下所示

Q1:设置字(时隙)长度的 ADC、ADC 是否可以读取 TDM 时隙?

Q2:关于设置 ADC 的通道时隙分配、以便 ADC 可以指定每个模拟通道数据到 TDM 时隙?

如有任何建议、请告知我。

谢谢。

此致、

劳伦斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、支持团队

我们看过应用报告:《 具有共享 TDM 和 I2C 总线的 SBAA415多个 PCm6xx0器件》

我们有2个问题、如下所示

Q1:设置字(时隙)长度的 ADC、ADC 是否可以读取 TDM 时隙?

Q2:关于设置 ADC 的通道时隙分配、以便 ADC 可以指定每个模拟通道数据到 TDM 时隙?

如有任何建议、请告知我。

谢谢。

此致、

劳伦斯

劳伦斯、您好!

Unknown 说:Q1:设置 Word (插槽)长度的 ADC、ADC 可以读取 TDM 插槽

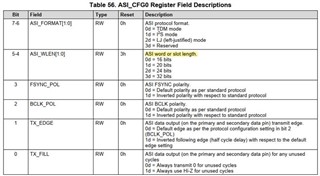

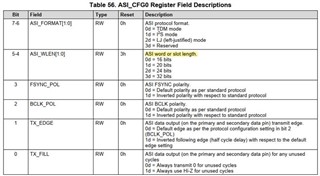

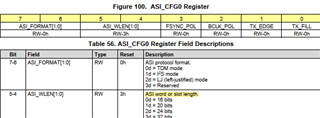

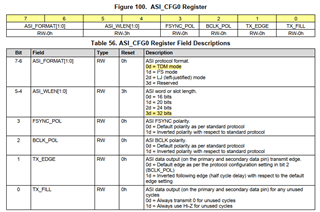

将 ASI 格式配置为音频输入数据。 您可以将 ASI 格式配置为字长为16位、但如果音频数据的长度为32位、则会截断。 反之亦然、器件会将数据附加0。

Unknown 说:2:关于设置通道时隙分配的 ADC,ADC 可以将每个模拟通道数据指定给 TDM 时隙

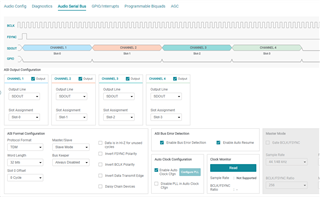

正确、通过 PPC3 GUI 更容易实现可视化、我建议在 ti.com/mysecuresoftware 上请求/下载以帮助实现此目的。

此致、

Daveon Douglas 您好、

我有两个问题。 我们只有 ADC、并希望配置 为采样率为48kHz 的 TDM8、BCLK 24MHz 和 FSYNC 48kHz。

首先、我想了解如何配置 TDM 时隙编号。 我在数据表中找不到任何寄存器来直接设置时隙编号。 我发现 ADC 依赖于主机处理器来提供 FSYNC 和 BCLK、并且我们可以配置字(插槽)长度。

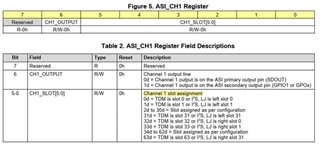

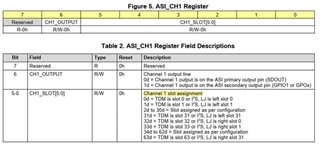

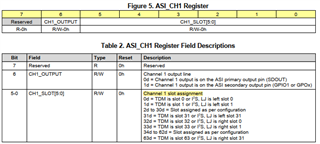

其次、我对向 TDM 插槽分配数据的过程很好奇。 根据数据表、其中提到通过配置 ADC 的通道时隙分配、ADC 可以指定应使用哪个 TDM 时隙来放置来自每个模拟输入通道的数据。 我的理解是否准确?

感谢您对这些问题的帮助。

首先,我想了解如何配置 TDM 插槽号。 我在数据表中找不到任何寄存器来直接设置时隙编号。

这是在页0、0xB 和0xC 中配置的。

分配允许 ADC 指定应使用哪个 TDM 插槽来放置来自每个模拟输入通道的数据。 我的理解是否准确?

正确、这在跨多个器件共享 TDM 总线的情况下很有用。 在器件1上、可以将 CH1和2配置为插槽0和1。 在器件2上、CH1和2可以占据时隙2和3、以此类推。 EVM 和 GUI 旨在支持 我们的6通道器件、但我们的所有 PCM6xxx0-Q1器件都是软件兼容的、 因此这就是寄存器映射中插槽数最多为64的原因。

下面是 PCM6240 (4通道) GUI 配置示例。

此致、

Hin、您好!

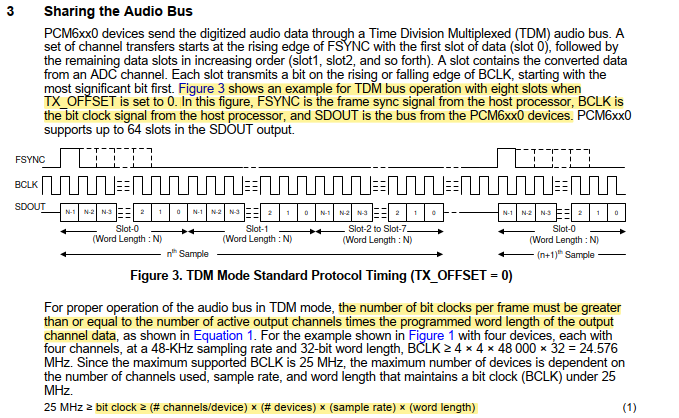

您之前链接的应用手册的第3节中提到了这一点。 该器件可支持每个器件(TDM8)多达8个通道时隙、并可通过提供的时钟进行配置。 BCLK 必须为≥(#个通道/器件)×(#个器件)×(采样速率)×(字长)、但不能超过25MHz 的最大 BCLK。 您可以提供一个支持最多8个通道的 BCLK、如果您仅使用一个 PCM6020器件 (即2个通道)、则剩余的6个通道插槽将为0。 如果您使用四个 PCM6020、则可以向0xB 和0xC 写入、以便为每个器件配置插槽、从而填充整个 TDM8数据线。

仅一个器件不支持 TDM16。 但例如、对于多个器件、请提供一个 BCLK =(8 CH) x (2个器件) x (48kHz) x (32位 WL) 24.576MHz、通过在1个 TDM 总线上级联两条数据线路来实现 TDM16。

此致、

感谢您的答复。 我想确认、要在一个 ADC 器件上配置采样速率为48KHz、字长为32位的 TDM 8格式、我需要:

1.将协议格式设置为 TDM 模式。

2.将字长设置为32。

3.向 ADC 提供48KHz 的 FSYNC 和12 MHz 的 BCLK。

该配置将允许 ADC 将其识别为 TDM 8格式、因为(12 MHz、BCLK)=(8、TDM 8)×(48KHz、采样率、FSYNC)×(32、字长)。

我的理解是否正确?