大家好、我们的团队:

我对 SRC4184IPAGT 和 CDCE913PW 有疑问

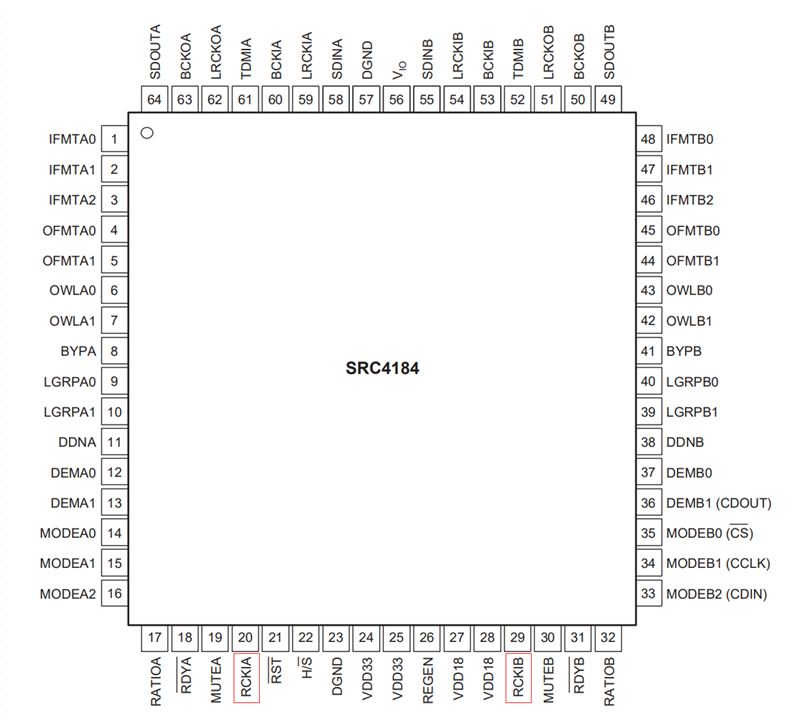

・SRC4184IPAGT

第1季度

是否存在任何与 RCKI 相关的交流工作条件?

例如、设置、保持以及与 BCKI/O、LRCKI/O、TDMiand 等同步。

第2季度

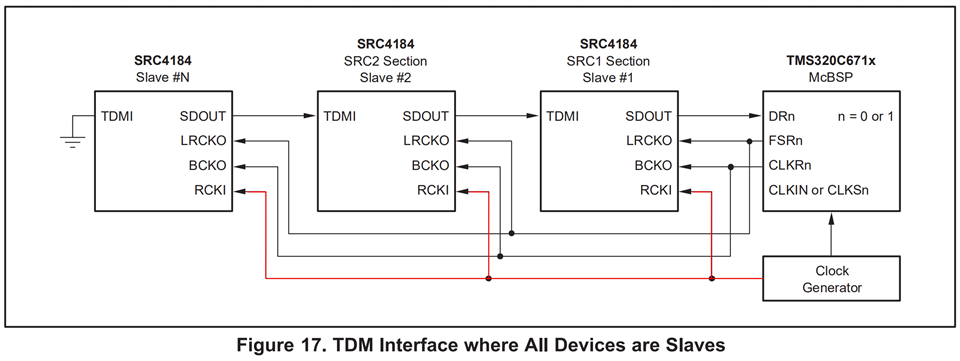

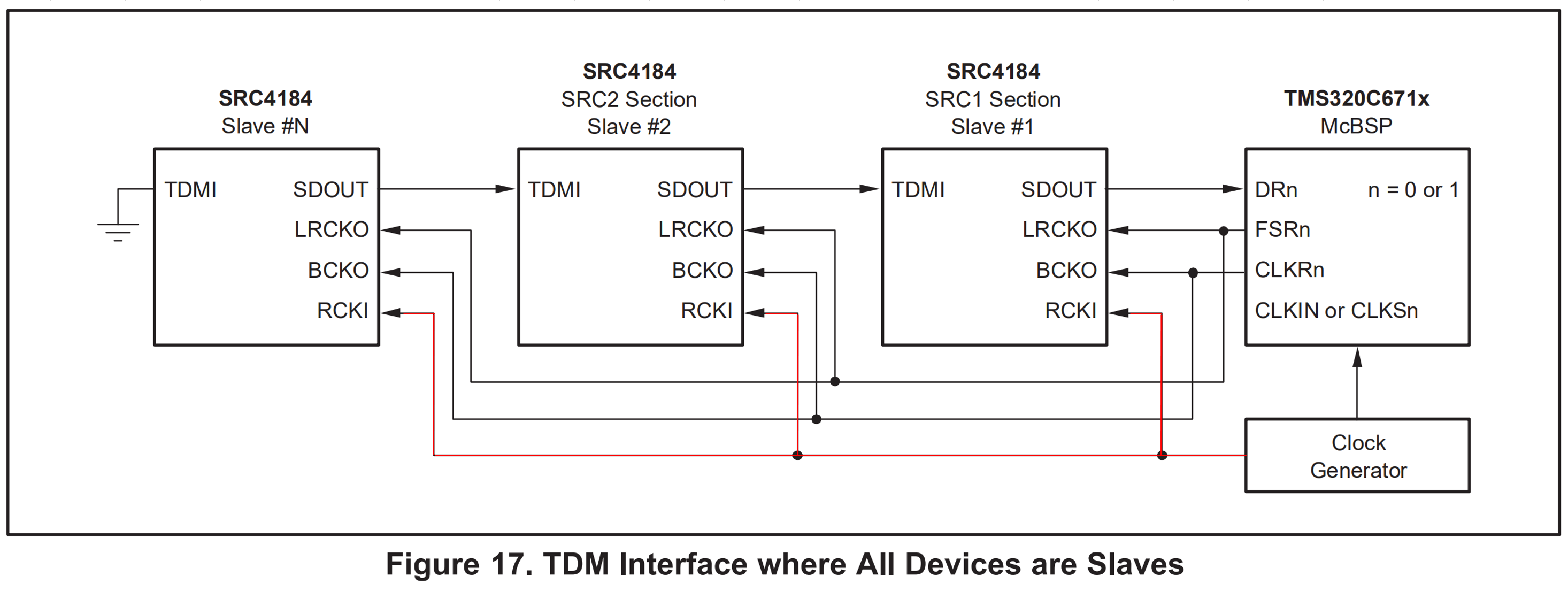

根据数据表中的图17、我可以看到 RCKI 信号输入到每个器件(SRC4184)、该器件在从模式下由1个时钟发生器控制、从而将线路偏离到3条线路。

我是否应该从1个时钟发生器偏离时钟信号? 我的意思是、我应该对 sysnc 中的每个器件都使用 RCKI 吗?

例如、如果将 CDCE913PW 用于时钟发生器、则由相同 Pdiv1制成的 CDCE913PW 输出 CLK 并连接如"Y1-SRC1/Y2-SRC2/Y3-SRC3"、是否存在任何问题?

・CDCE913PW

第1季度

当该偏离设置为使用 Pdiv1中的 Y1、Y2、Y3时、Y1与 Y2/Y3之间是否存在任何延迟?

第2季度

为什么在仅使用 Y1时和使用 Y1/Y2/Y3时,尽管使用相同的 Inclock 和相同的输出频率设置, PLL 的 M、N、freq 在 Clock Pro 中存在差异。

我想从用于 Y1设置的 Pdiv1中将 Y2/Y3设置为使用没有变化。

总之、在这种情况下、该器件使用 Y1/y2/Y3相同的频率和相同的 Pdiv、我可以使用寄存器设置参考时钟专业版中的 BitViewer、可以吗?

第3季度

在 Clock Pro 中,为什么我在 BitViewer 中看不到 reg15 nad 31 ?

问题4

如果我将 reg"EEWRITE"设置为1以便将数据保存到存储器中、是否在不使用 reg"EELOCK"设置的情况下立即将 reg"EELOCK"设置为1?

感谢您的支持