Other Parts Discussed in Thread: PCM1808

大家好!

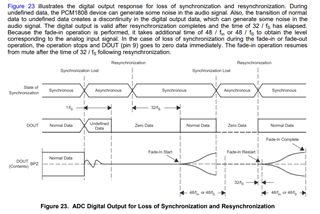

我尝试使用 PCM1808读取模拟信号、遇到一个非常奇怪的问题。 我向芯片馈送一个正弦波(以2.5V 为中心)、通过 I2S 接口读回严重失真的信号。 更令人困惑的是、失真似乎高度不对称、波形的"负半部分"的失真要大得多。 以下是 I2S 数据的屏幕截图:

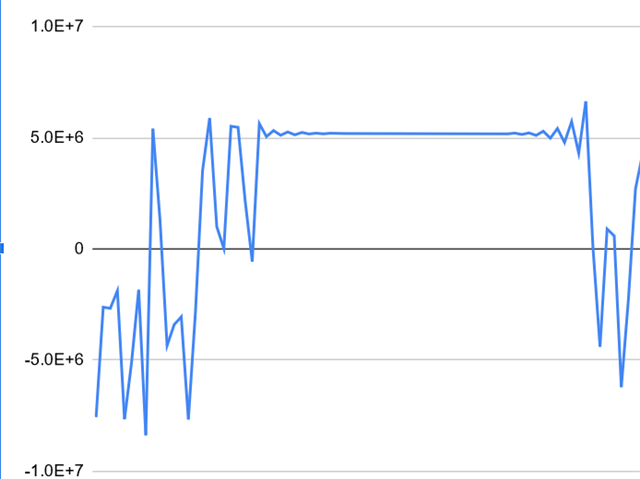

作为完整性检查、这里是直接记录在芯片上的输入信号。 2.5Vpp 1kHz。

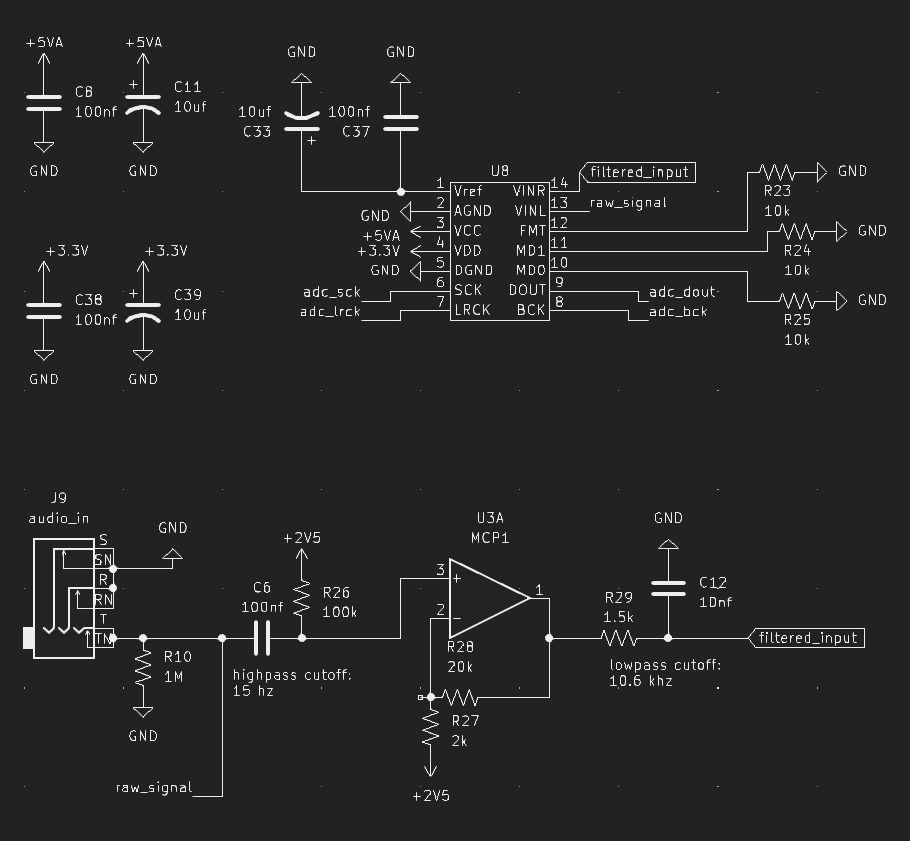

我的设计基本上只是参考设计、并且我已经验证了电源/接地电源是稳定的。

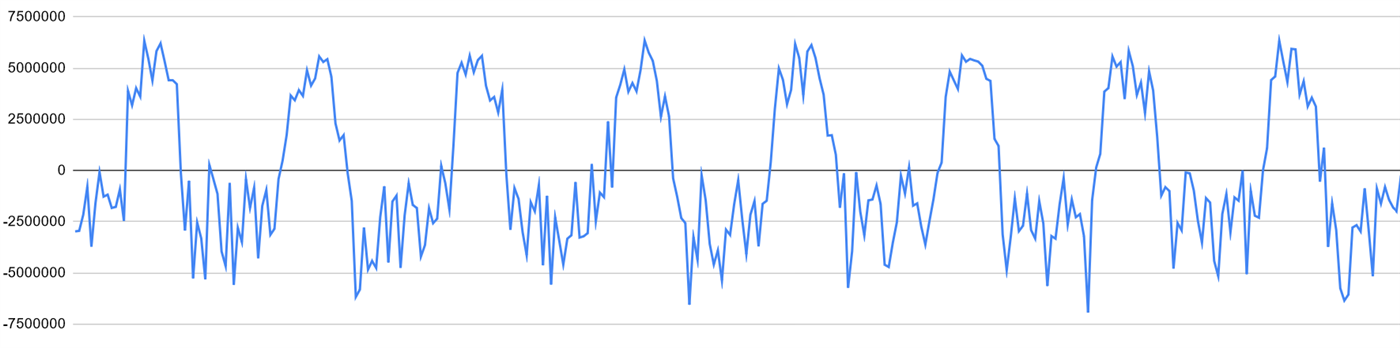

我还注意到、在点处、输入似乎"冻结"并出现振铃。 奇怪的是、这种振铃似乎发生在冻结部分的开始和结束时、好像它能够预测"解冻"、便会认为芯片内部出现了问题? 下面是馈入较慢的100Hz 正弦波时的 I2S 数据图。 如您所见、它似乎冻结了~100个样本、并在开始和结束时响铃:

我真的不知道发生了什么-我几乎会倾向于假设我有一个损坏的零件/板,除了事实,我有两个他们的行为相同. 如果有人以前见过这样的东西,或可以建议任何尝试,请告诉我!

编辑:这里是我的原理图的相关部分、包括输入放大。 如您所见、它与参考实现几乎相同。 我看到两个输入的行为都是相同的(原始和11x 放大)、但上面的屏幕截图来自放大源。 我还尝试在信号和芯片输入引脚之间添加一个0.1uf 电容、以查看是否会产生影响、但这并没有解决问题。

谢谢!