https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1354246/pcm3060-external-reset-operation

器件型号:PCM3060嗨、团队:

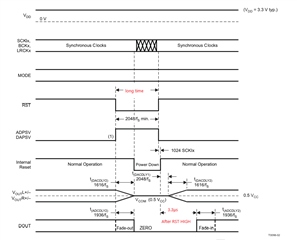

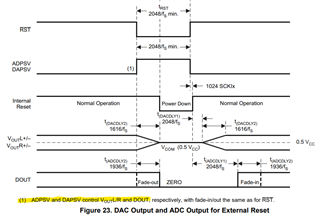

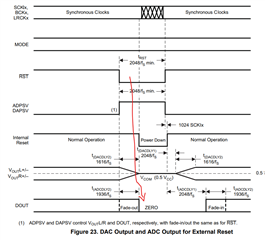

我想、应用外部复位时、内部复位会在 RST 引脚变为高电平时返回、DOUT 延迟会从此处开始、但当我实际操作时、一旦 RST 引脚变为高电平、DOUT 就会立即输出。

这是否意味着 RST 引脚变为低电平、在2048/fs 后、无论 RST 引脚如何、ADPSV 和 DAPSV 都变为高电平、从而返回内部复位并启动延迟?

此致、

柳。