请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV320AIC3105 工具与软件:

您好、先生、

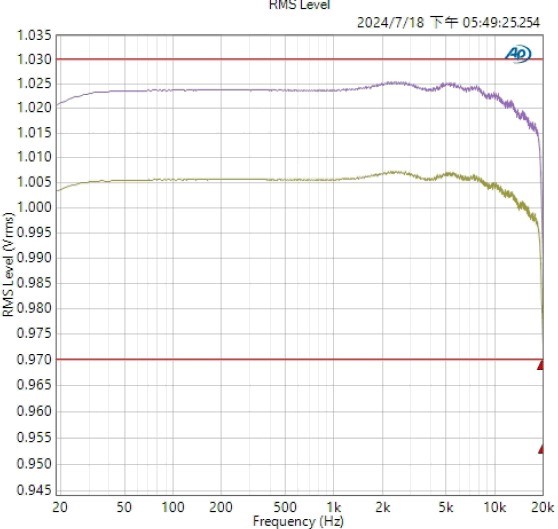

我的客户正在验证数字内插滤波器的器件特性。 他们发现、只有旁路通道(line2)可满足通带测试结果0.45fs (Hz)。 是 PLL 配置问题吗?

下面是客户 PLL 配置。

MCLK= 24.576MHz

LRCK= 48KHz

16位数据

P= 2

Q= 4

J= 8

D= 0

R= 1

下图是在 Line1通道中进行的测试。