Other Parts Discussed in Thread: DRV595

工具与软件:

大家好!

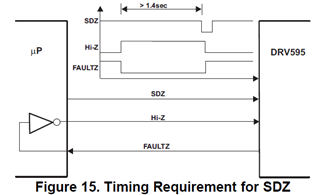

根据数据表的绝对最大额定值、 SDZ 的最大压摆率 为10V/ms。

此外、看来是由于目前的限制而引起的注(2)写如下:

如果超过最大压摆率、则需要100 kΩ 串联电阻。

MAXMUM 压摆率受限的原因是什么?

当使用 CPU 直接控制 SDZ 时、有必要通过速率来保护这一点吗?

在这种情况下、是否需要一个100k Ω 的串联电阻?

启动电源后、SDZ 固定为低电平。

此致、

Toshi