Other Parts Discussed in Thread: PCM4202, TLV320ADC5120, TAA5212

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1420479/pcm4202-period-of-lrck-and-bck

器件型号:PCM4202主题中讨论的其他器件: TLV320ADC5120、 TAA5212

工具与软件:

尊敬的专家:

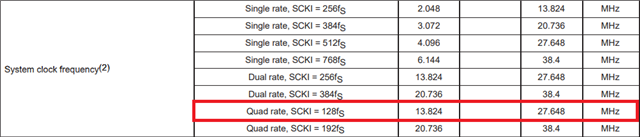

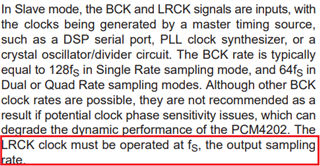

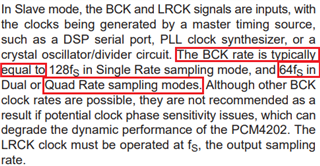

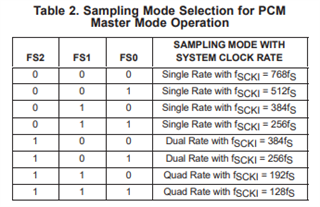

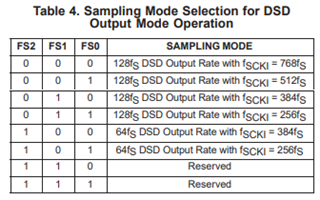

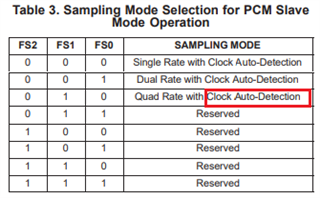

我们要将 PCM4202设置为 PCM 从模式和四倍速率、并以210.9kHz 的采样率运行。

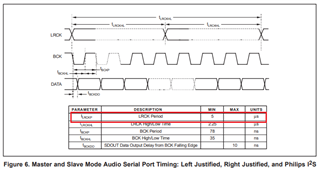

在这种情况下、tLRCKP=4.748us (=1/210.9kHz) tBCKP=74.19ns (=tLRCKP/64)。 是否有任何违规行为?

请参阅数据表

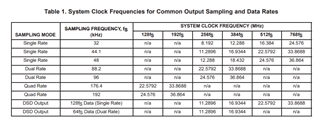

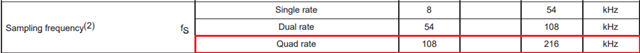

P14 (等) 说明最大采样率为216kHz、因此我们认为210.9kHz 在该范围内。

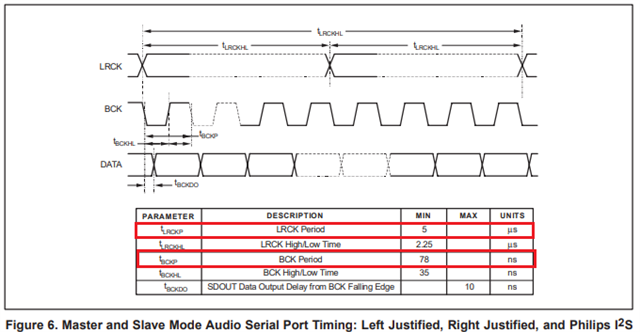

一方面、图6表明 tLRCKP=min 5us (tBCKP=min 78ns)、

我们感到困惑的原因是、最大采样率可以被读取为200kHz (=1/5us)。