请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TAD5142 工具与软件:

在"7.3电源建议"中、有以下陈述:

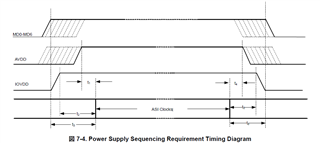

'对于电源断电要求、T4、T5和 T6必须至少为10ms。'

我的电路无法满足上述要求。

主机端无法检测 IOVDD 和 AVDD 的下降沿。

因此、T4至 T6为0ms。

这是否会导致 IC 在关闭电源时发生故障、或者重新启动时是否会出现异常行为(如果关闭电源5秒或更长时间)?

*据我所知,我认为以下的要求是不能满足的。

"该时序(如图7-4所示)允许器件缓慢降低回放数据的音量、关闭模拟和数字块、以及将器件置于低功耗模式。"

我认为上述措施可以防止掉电期间出现线路噪声、但在我的电路中、我们针对输出放大器侧采取了措施。