主题中讨论的其他器件:TLV320ADC3140

工具与软件:

您好:

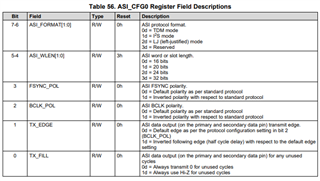

当前使用的 I2S IP 需要 TDM 模式、并且 SCLK (时隙时钟)必须为32。 因此、48K/16bit/4通道格式录制所需的最小 SCLK 为3.072M。

I2S 具有相应的寄存器、这些寄存器被配置为在一个时钟周期内对指定的时钟门控有效、例如32位、但实际的输出时钟信号是16位。

我想知道 TLV320adcx140编解码器的调整应该如何配置寄存器来满足此 I2S 要求

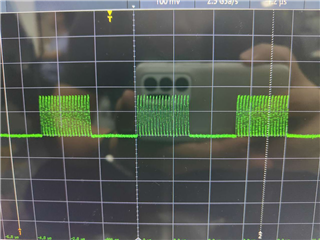

如下32位时隙 BCLK: 16位 BCLK + 16位低电平

将 传输16位音频采样

非常感谢