https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1462681/tas3251-clicking-noise

器件型号:TAS3251工具与软件:

大家好、我们将 TAS3251用于 BTL 和 PBTL。 播放音乐时、PBTL 中会出现咔嗒声。 您能帮助分析原因吗?

原理图:

e2e.ti.com/.../AMP-EV1-2024_2D00_12_2D00_20.pdf

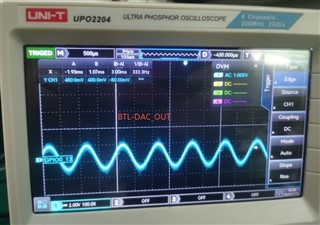

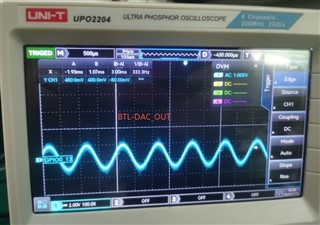

测试波形:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1462681/tas3251-clicking-noise

器件型号:TAS3251工具与软件:

大家好、我们将 TAS3251用于 BTL 和 PBTL。 播放音乐时、PBTL 中会出现咔嗒声。 您能帮助分析原因吗?

原理图:

e2e.ti.com/.../AMP-EV1-2024_2D00_12_2D00_20.pdf

测试波形:

大家好、我正在从事同一个项目。

我们当前不使用内部 DSP、未将配置加载到芯片中。

这只是从扬声器终端获取音频的基本寄存器配置。 立体声 BTL 芯片工作正常。

两个放大器具有相同的寄存器配置。

我注意到、DAC_AVDD 对于 PCB 布线似乎非常合理、从3V3 LDO 到引脚56、而不与另一个 IC 共享 PCB 引线、似乎可以减少尖峰。 除了残余 LDO 噪声外、我在 AMP_3V3上看不到任何可见噪声/尖峰。

有趣的是、如果我用稻草将盖吹到 PCB 区域、将电容器装到 DVDD、AVDD 和 C_START、则尖峰会暂时增加。

与立体声 BTL 相比、PBTL 模式下的 TAS3251是否会从功率级辐射更多的噪声?

您能否确认我们在主/从模式和 BTL/PBTL 模式下配置 IC 的方式在电气上是正确的?

我感觉 A/B 两个级相互切换、它们会产生更高的噪声、这会被芯片的 DAC 部分拾取。

在 PCB 上、引脚34和引脚39连接在 IC 下方、不像数据表建议的那样靠近输出电感器。 您是否认为这可能是一个问题?

谢谢

您好、Francesco、

大多数情况下、原理图看起来都很好。 GVDD_A 上的旁路电容可能更大(数据表中为330nF)、但这不会导致问题。 如果它导致两个输出之间严重不匹配、则可能会导致问题。 我在最近的示波器上注意到 I2S 时钟并不是很干净、在这种情况下、您的来源是什么? 此外、在发送的第一个屏幕截图中、噪声似乎是仅在 PBTL 通道中发生的突发。 该点击是否会持续发生?如果不会、第一次出现时会执行什么操作?

此致、

Ramsey

在 TPS3251EVM 上、GVDD 引脚的旁路电容为100nF。 无论如何、我尝试了1uF 并使用一根导线将串联0r (R2和 R3)短接、但没有改善。

我还减少了 I2S 总线上的串联电阻以提高信号完整性、但却没有改善噼啪噪声。

噼啪噪声只是随机的,它似乎在某种程度上与音量水平成正比。 没有什么特定的东西可以触发它。

TAS3251中的 DAC 是否对来自功率级的开关噪声敏感?

PCB 布局中是否有什么地方在 PBTL 模式下需要特别注意?

您好、Francesco、

无论 BTL 和 PBTL 如何、器件的行为都相同。 唯一真正的区别是输出的驱动方式、使得两个通道可以连接在一起。 由于同时存在数字侧和高电流侧、因此不良布局经常会导致问题、因此器件本身确实需要进行布局设计。 但是、随机和中间点击对我来说更像是发热、物理(比如连接不良)或输入数据问题。 当发生这些情况时、您能否检查 FAULT 和 OTW 引脚? 此外、如果您有串行数据监视器(如 AP)、您可以探测数字输入以确保数字数据符合预期吗?

此致、

Ramsey

实际上、我对布局设计存有疑问。

在散热方面、芯片上安装了一个大散热器、即使在器件处于冷态时也会出现这种噼啪声。

这种情况也会发生在我们制作的所有样片上、因此我倾向于排除组装或连接问题。

我尚未检查 OTW、但我怀疑该引脚是否会被触发。

我不需要 AP 来检查数字数据(我拥有也可以检查)、但另一个 BTL 放大器 IC 使用完全相同的 I2S 数据、并没有显示问题、因此我倾向于把问题排除在 I2S 数据流中。

我们将使用4线从器件 I2S 输入模式、我的理解是在此配置中仍需使用 PLL、芯片应配置为自动时钟设置。 是这样吗?

我想知道在存在来自功率级或电源布线的高电场的情况下 PLL 是否会暂时失去锁定。

PLL 由哪个电源引脚供电?