主题中讨论的其他部件: PMP

工具/软件:

尊敬的 TI 支持团队:

我们将使用 TI-RTOS 开发 CC2651R3SIPA 固件、一些中断处理程序实现为零延迟 ISR (即绕过 RTOS 内核)。 安装这些处理程序的方法是直接修改 NVIC 矢量表、而不是使用`intRegister ()`来避免中断 OS 管理的中断。

我们知道 ARM 勘误表838869、我们想确认我们的实施是否受到影响。

在我们的一个零延迟 ISR (GPT0A)中、我们在 ISR 结束时对 ADC 寄存器(AUX_ANAIF:ADCTRIG)执行存储操作。 存储发生在调用以下设置函数`pmp_tswTimerStart ()`后,这会设置计时器和其他配置。

以下是设置函数`pmp_tswTimerStart ()`的相关代码:

```c

void pmp_tswTimerStart (PMP_EXEC_t* p_exec)

{

Power_setDependency (PowerCC26XX_Periph_GPT0);

//停止计时器

TimerDisable (GPT0_BASE、TIMER_A);

//防止转换到待机或空闲状态

Power_setConstraint (PowerCC26XX_SB_disallow);

Power_setConstraint (PowerCC26XX_IDLE_PD_disallow);

//将计时器设置为 PWM 模式

TimerConfigure (GPT0_BASE、TIMER_CFG_SPLIT_PAIR | TIMER_CFG_A_PWM);

TimerLevelControl (GPT0_BASE、TIMER_A、TRUE);//设置为低电平启动

//设置周期

TimerLoadSet (GPT0_BASE、TIMER_A、p_exec->Tswus);

TimerMatchUpdateMode (GPT0_BASE、TIMER_A、TIMER_MATCHUPDATE_NEXTCYCLE);

//清除中断

TimerIntClear (GPT0_BASE、TIMER_CAPA_EVENT);

//手动更新向量表以寄存器 ISR

uint32_t ui32value;

ui32value = HWREG (NVIC_vtable);

HWREG (ui32value +(INT_GPT0A * 4))=(uint32_t) pmp_intTsw;//直接设置矢量表条目

//启用中断

IntPrioritySet (INT_GPT0A、INT_PRI_LEVEL0);

TimerIntEnable (GPT0_BASE、TIMER_CAPA_EVENT);

IntEnable (INT_GPT0A);

//为执行状态设置标志

p_exec->TpdValid = true;

p_exec->enableDrive = true;

//启动计时器

TimerEnable (GPT0_BASE、TIMER_A);

}

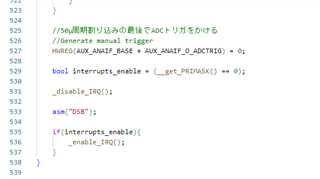

以下是零延迟 ISR 的相关代码(pmp_intTsw):

void pmp_intTsw (void)

{

// ISR 逻辑……

//在 ISR 的最末尾、我们手动触发 ADC

HWREG (AUX_ANAIF_BASE + AUX_ANAIF_O_ADCTRIG)= 0;//手动 ADC 触发

}

我们对以下情况感到关切:

对 NVIC 矢量表进行直接修改的零延迟 ISR:我们使用零延迟 ISR、其中我们直接修改 NVIC 矢量表、不使用 IntRegister ()。 此实现方式是否正确、或者这是否会导致与 ARM 勘误表838869相关的任何问题?

ISR 中的 ADC 寄存器写入:具体而言、在 ISR 结束时对 ADC 寄存器(ADCTRIG)的写入是否符合 ARM 勘误表838869中所述的条件:在这种条件下、具有等待状态的外设寄存器的存储可能会导致错误的中断矢量控制?

请确认:

如果此 ADC 寄存器写入可能会受到勘误表的影响?

使用零延迟 ISR 是否会触发勘误表中提到的问题?

如果需要、我们可以提供更多详细信息或完整实现。

感谢您的支持。

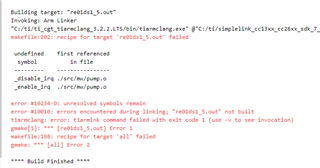

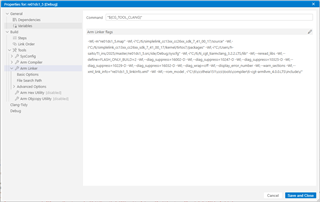

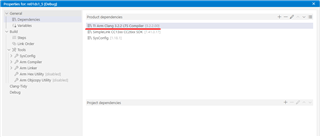

我的工程属性

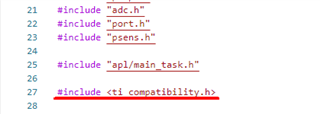

我的工程属性  我的代码标头

我的代码标头  我的代码中的 ISR 到此结束。

我的代码中的 ISR 到此结束。