工具与软件:

早上好、

我的工程存在功耗问题、我发现工程和示例工程 basic_ble_LP_EM_CC2340R5_freertos_ticlang 存在相同的问题。

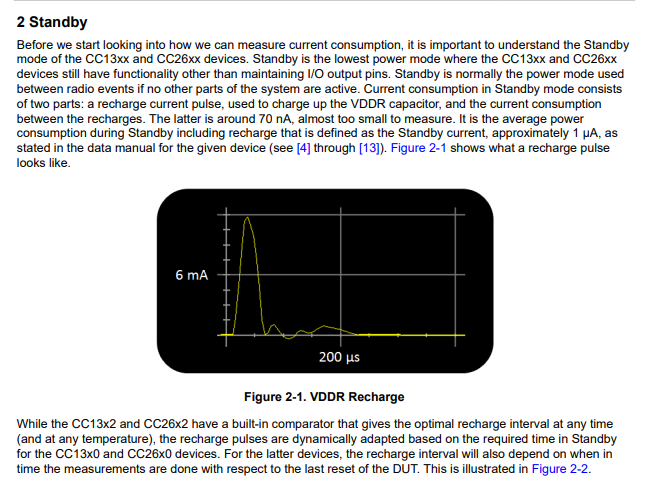

我在 TI 文档中阅读到、在对 VDDR 容量再充电时、电流在待机状态出现峰值。 这些峰值应最大为70nA。

但是、在带有定制项目的电路板和带有 basic_ble_LP_EM_CC2340R5_freertos_ticlang 的演示板上、我们观察到40 mA 的峰值。

我们使用 simplelink_lowpower_f3_sdk_8_10_01_02

CC2340R5开发套件

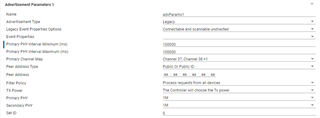

要重现这些峰值、请导入 basic_ble_LP_EM_CC2340R5_freertos_ticlang、您只需增加广播以切换到待机模式即可。 在本例中、我选择了一个非常大的数字100,000、以确保观察峰值并为低频时钟源设置 LF RCOSC

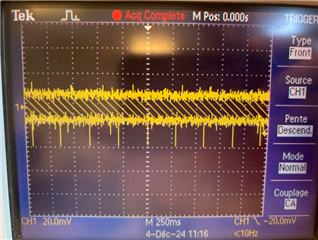

图片、此处有一个10欧姆电阻器与电源串联(压降为20mV、即2mA 消耗)。

同样、也可以通过专门用于消耗的测量器件观察到。

我们的目标是抑制这些峰值或将其降低到文档中指定的70nA。

我们怎么能做到这一点?

此致

Yohan