工具/软件:

尊敬的支持团队:

我与 Mcan Peripheral 合作过、在回答问题之前、我先做了介绍。

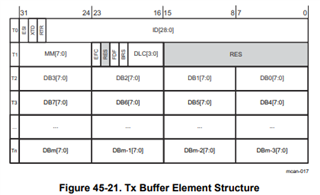

根据文档 SPRUIZ1B、在图35-21 第5216页中绘制的 TX 缓冲器元素结构适用于

- 传统 CAN 外围设备:FDF = 0

- FD CAN 外围设备:FDF = 1

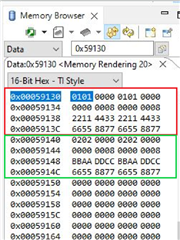

根据 TI API 和 TI 示例"mcan_EX7_classical_transmit.c" 、函数 MCAN_writeMsgRam 用于填充 C 结构 MCAN_TxBufElement、其数据字段为

uint16_t DATA[MCAN_MAX_PAYLOAD_Bytes];

#define MCAN_MAX_PAYLOAD_Bytes (64U)

上述结构在"RAM TX 缓冲区"上分配、 在"FD CAN"中被称为 TX 缓冲区、在"传统 CAN 外设"中 被称为 TX 邮箱。

关于将 MCAN 外设用作"传统 CAN 外设" 并由 TI API 驱动的考虑因素是: 对于在 RAM 中分配的每个 TX 缓冲区、 都会发生浪费(64-8 )=56字节的情况。

我的考虑是否正确?

如果是、TI API 中是否有一个 MAX_PAYLOAD_BYTES 等于8的 TX 缓冲区元素 C 结构、及其相关的 C 函数将其分配为"标准 TX 缓冲区元素"?

我将避免上述浪费和使用带有 API 功能的 Mcan 外围设备。

感谢您的支持、

Ettore