工具/软件:

您好、

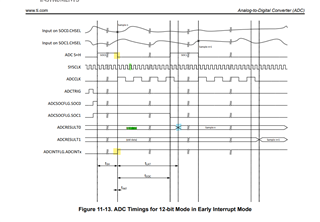

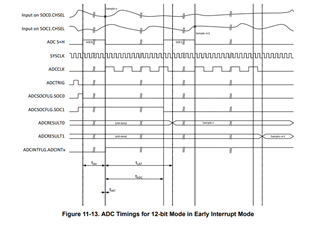

我最近考虑了 Silicon errata sprz412n、我很难理解这一点 "ADC:DMA 读取过时结果" 特别是在可视化调度方面。

根据我在详细信息部分中的理解、 ADCINT 在采集结束前触发、这可能会导致上一周期的数据过时。 我的说法是否正确、因为这只会影响的数据 配置 直流/直流转换器 ADCINT (以及后续 SOC -但这不会被视为异常行为)?

对我来说、令人困惑的是 权变措施 部分。 使用"虚拟 DMA"引入延迟似乎有点极端、这使我认为我可能不完全理解该通报。

由于我们已经使用所有 DMA 通道、但并非所有 ADC SOC、因此我们考虑使用"虚拟 SOC"来触发 ADCINT 进而触发 DMA 的 PWM 信号。 您能否确认这是正确的解决方法?

谨致问候、BR