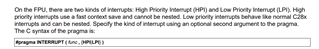

工具/软件:

我将 EPWM1A 配置为在 TBCTR=0时变为高电平

其中100MHz SYSCLK 和分频器设置为/1

我将 ISR 配置为在 CMPB=10时触发 (例如、我尝试了不同的值)。 在 CMPB=10时、我预计 ISR 将在0.10us 时触发、再加上一些中断延迟。

我在 EPWM1a 的上升沿与在 ISR 中设置的调试引脚之间看到了类似5.37us 的内容。 我知道在触发中断和 ISR 执行开始之间存在一些中断延迟、但在5us 后似乎很高。

在 TBCTR=CMPBU 上、我应该预期什么类型的中断延迟?

下面是时序屏幕截图和一些相关代码片段。

EPWM_setClockPrescaler (EPWM_DATA_PTR->EPWM_BASE、EPWM_CLOCK_DIVIDER_1、EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBaseCounterMode (PC_EPWM_PTR->EPWM_BASE、EPWM_COUNTER_MODE_UP);

EPWM_setActionQualifierAction (PC_EPWM_PTR->EPWM_BASE、EPWM_AQ_OUTPUT_A、EPWM_AQ_OUTPUT_HIGH、EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction (PC_EPWM_PTR->EPWM_BASE、EPWM_AQ_OUTPUT_A、EPWM_AQ_OUTPUT_LOW、EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setCounterCompareValue (EPWM_DATA_PTR->EPWM_BASE、EPWM_COUNTER_COMPARE_B、10);

EPWM_setInterruptSource (EPWM_DATA_PTR->EPWM_BASE、EPWM_INT_TBCTR_U_CMPB);

__interrupt void epwm1_isr (){

GPIO_writePin (124、1);

EPWM_clearEventTriggerInterruptFlag (EPWM1_BASE);

INTERRUPT_CLEARACKGROUP (INTERRUPT_ACK_GROUP3);

GPIO_writePin (124、0);

}

I 还启用了死区、DBRED=DBFED=40 (高电平有效互补)