工具/软件:

客户如下设置 PWM 逻辑:

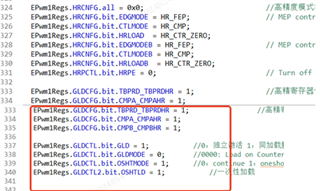

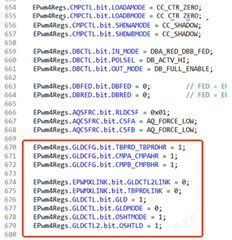

1、 PWM1通过计数器归零事件产生的通用 SYNC 信号到 PWM4、PWM1和 PWM4都会清除计数并通过 SYNC 事件更新寄存器

2、 PWM1和 PWM4都设置为带计数器区域事件的全局一次性加载、PWM4链接到 PWM1

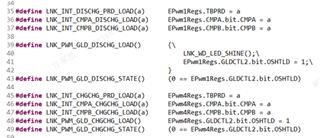

3、 Timer0常规40kHz 中断、以便更新 PWM1和 PWM4的 PWM 频率和占空比、然后触发全局一次性加载

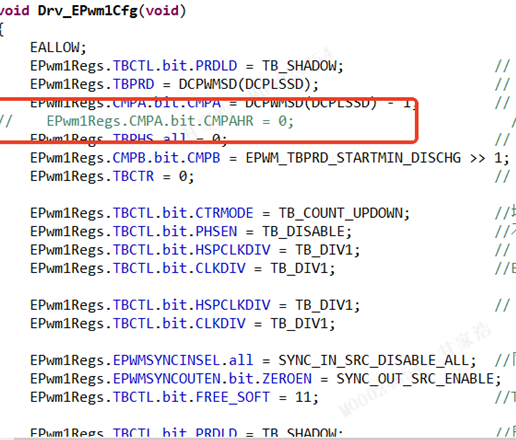

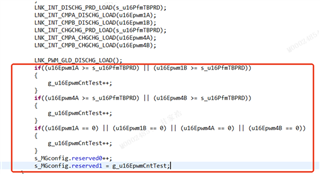

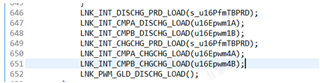

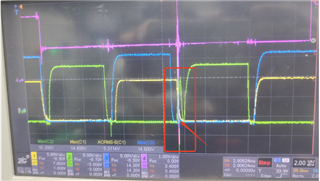

如果按如下方式执行步骤3代码、则会出现一般异常波形

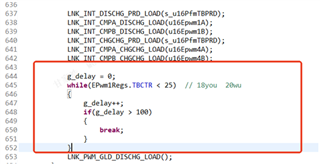

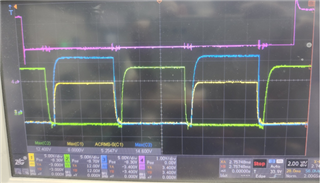

如果步骤3代码按如下方式进行修改、以避免在计数器为零时接近更新、则 PWM 波形始终运行良好

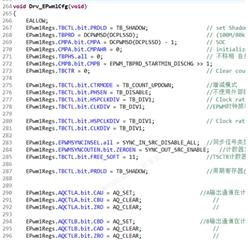

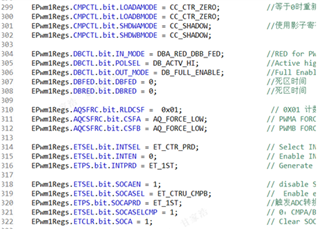

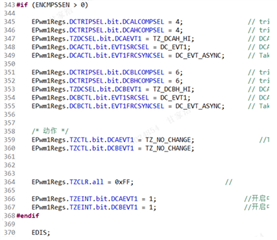

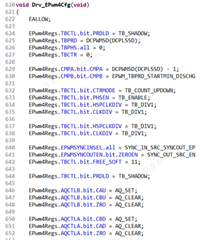

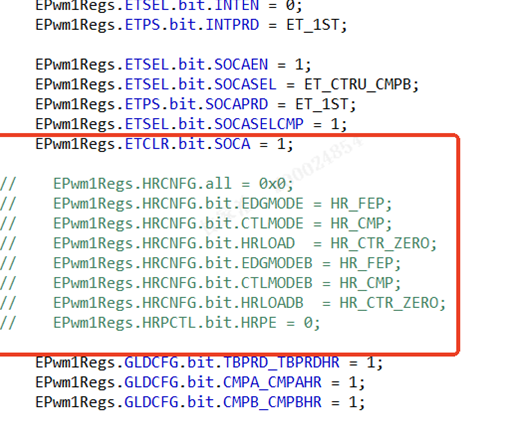

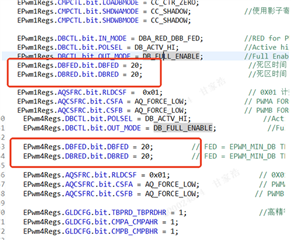

下面是 PWM1和 PWM4设置代码、您能帮助查看是否缺少任何设置而导致问题吗?