工具/软件:

尊敬的专家:

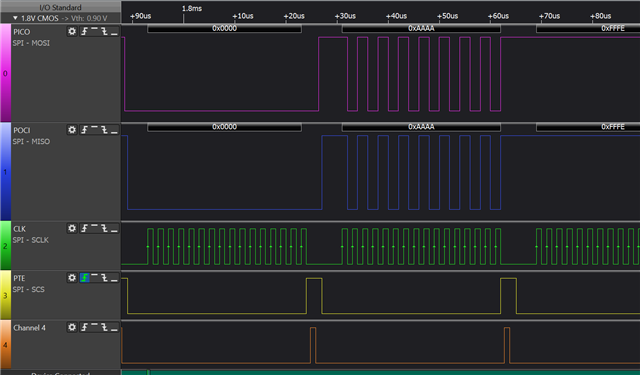

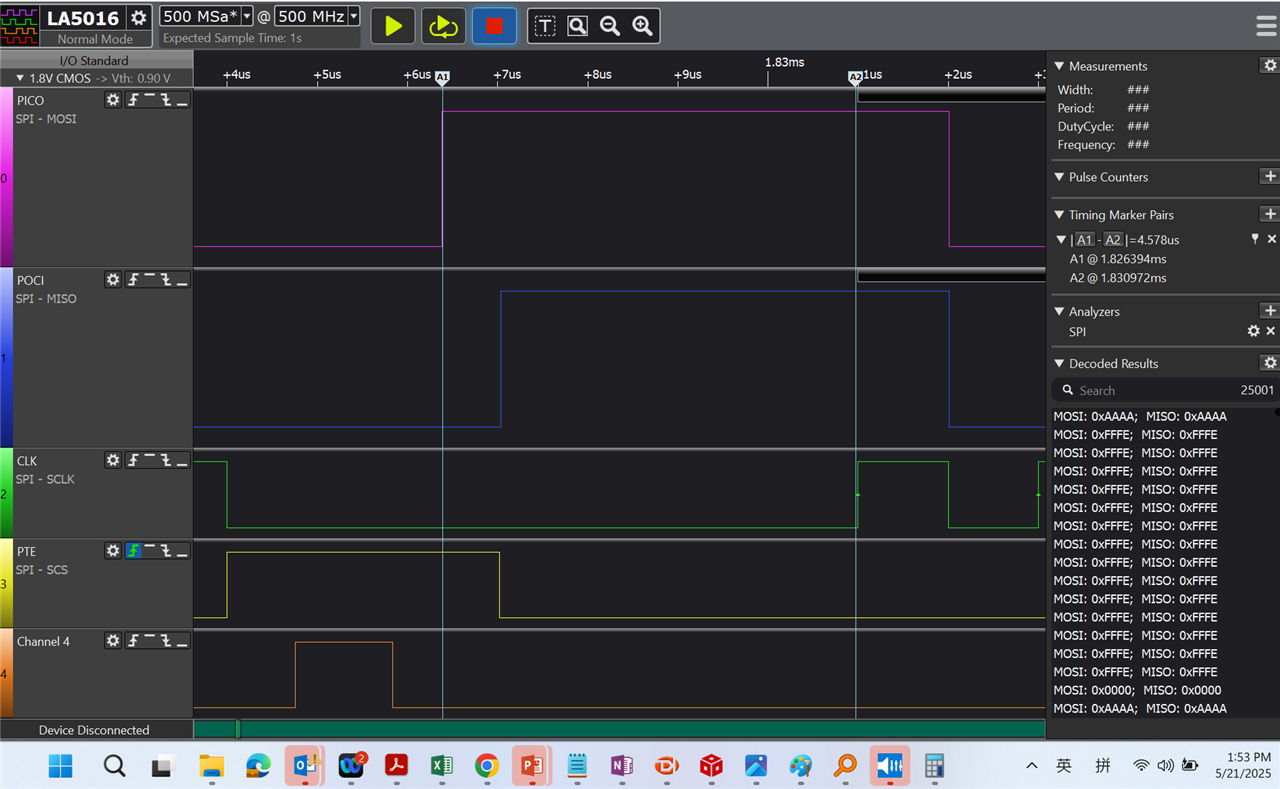

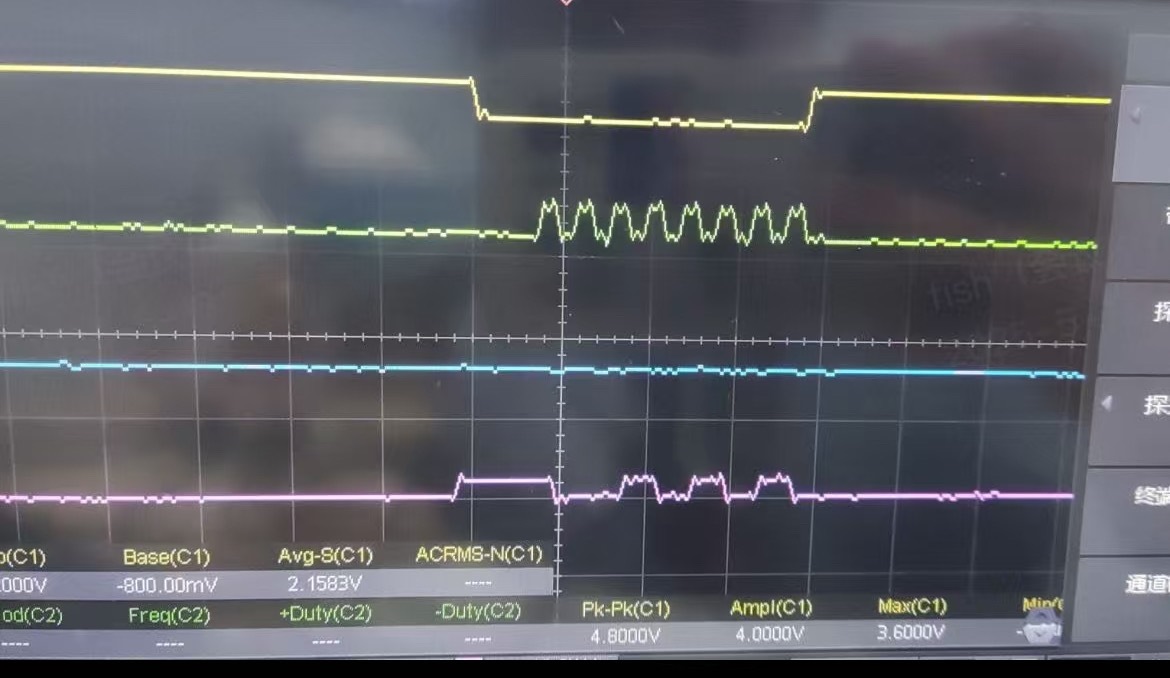

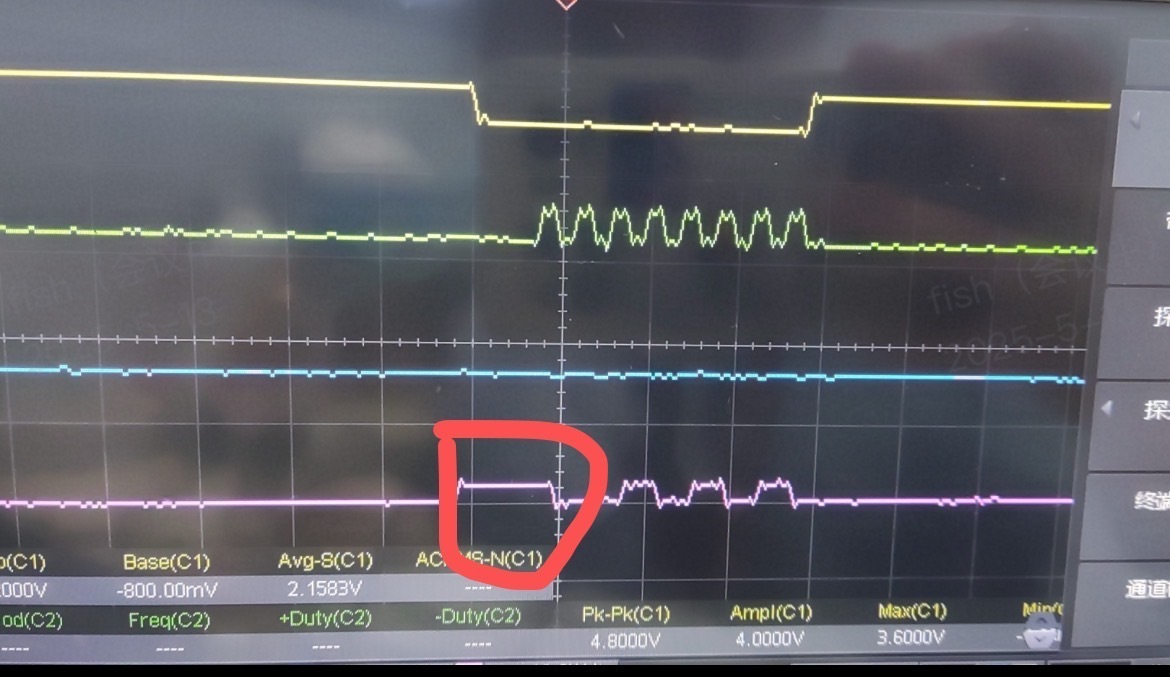

美好的一天! 我要找客户。 28P65用作 SPI 主器件。 我的客户发现、在她的 SPI 范围内、当 PTE 为低电平并且 CLK 无法启动时、SIMO 将立即被驱动为高电平。 我用红色圆圈标记了奇怪的部分。 波形 从上到下依次为 PTE、clk、SOMI、SIMO。

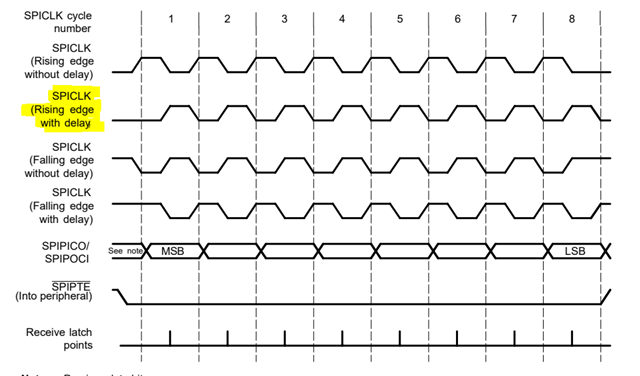

我已经检查了标准的 SPI 范围、 当 PTE 被驱动为低电平时、SIMO 不应立即通过 PTE 跟踪更改、而应跟随 CLK。

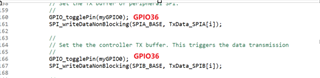

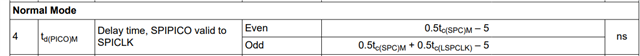

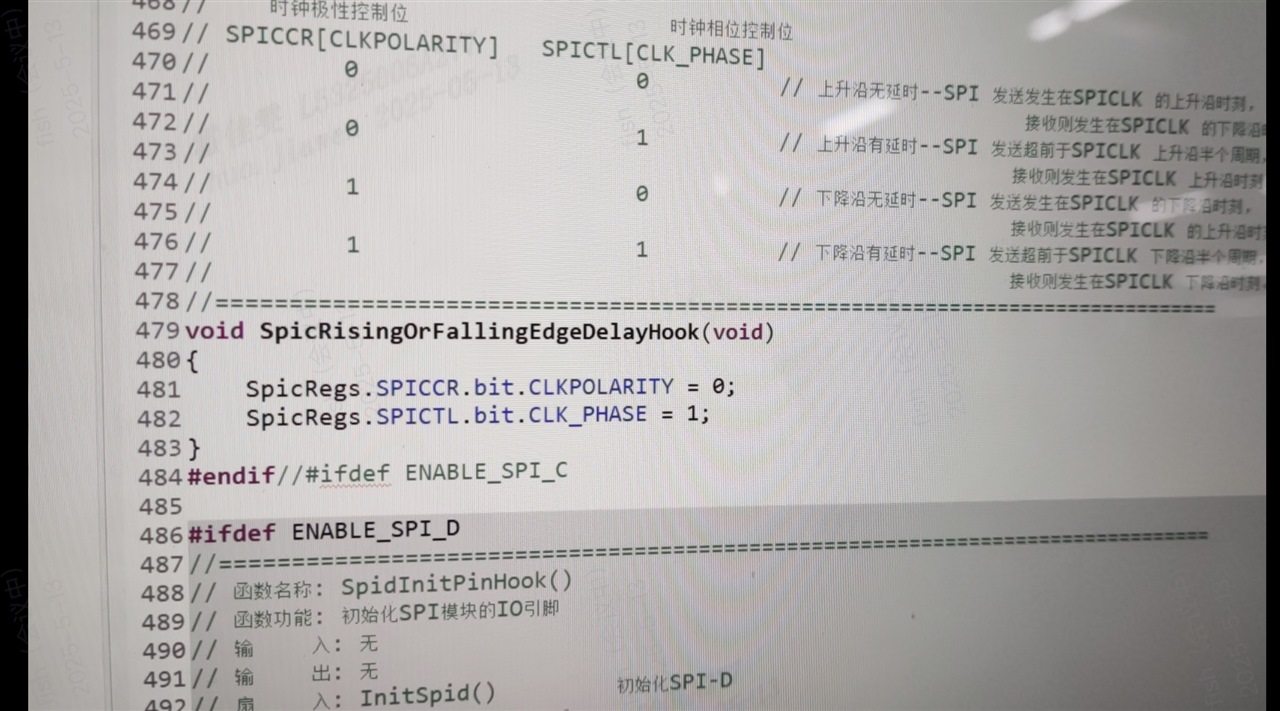

这是相位和极性配置。

你能帮助解释这个现象吗?

这是一个紧急情况、您能帮助尽快检查吗?

谢谢!

此致

Kita