主题:C2000WARE 中讨论的其他器件

工具/软件:

您好、专家

异常描述:

模块无法正常运行、缺陷率为每 100 件 1 件。

分析过程:

1、目视检查发现没有问题。

2.芯片重新编程成功。

3、对周边电路模拟信号和电源电压进行测试,未发现异常。

以下信号经过测试并确认正常:

① 引脚 22 (Iout+):~1.55V(正常)

② Ω PIN8 (VCCSEN):~1.69V(正常)

③ Ω PIN6 (VIN_S):~1.44V(正常)

④ PIN23 (VTEMP):~2.99V(正常)

⑤ 引脚 16 (VO_S) 和引脚 21 (ADC_A4):~0V(正常)

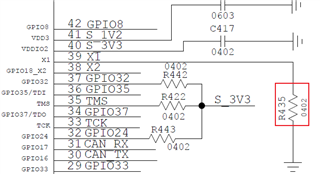

⑥ Ω PIN20 (S_3V3):~3.3V(正常)

4、软件工程师艾登在程序测试中发现错误的时钟时间。

① 首次测试

GPIO 配置测试:

PIN-4-XRSN:稳定高电平;PIN-31-GPIO17 脉冲周期:100μs;Pin36-GPIO35 脉冲周期:8μs

测试结果:

在常规模块中、脉冲周期与定义的值相匹配。 在故障模块中、脉冲周期为:PIN-31-GPIO17:1000μs;Pin36-GPIO35:80μs。 故障模块中的所有时间都比正常时间长、并且看门狗不断复位。

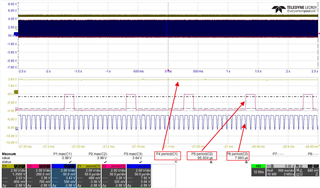

如下所示:

正常模块

C1(黄色:复位信号 XRSN)、C2(红色:GPIO17)、C3(蓝色:GPIO35)

异常模块

C1(黄色:复位信号 XRSN)、C2(红色:GPIO17)、C3(蓝色:GPIO35)

② 第二个测试

为了确定模式、测试程序中的脉冲周期增加了一倍、并比较了正常模块和异常模块之间的差异。

GPIO 配置测试:

PIN-4-XRSN:稳定高电平;PIN-31-GPIO17 脉冲周期:200μs;Pin36-GPIO35 脉冲周期:16μs

测试结果:

在常规模块中、脉冲周期与定义的值相匹配。 在故障模块中、脉冲周期仍然存在:PIN-31-GPIO17:1000μs;PIN36-GPIO35:80μs。 故障模块中的周期没有改变、并且看门狗不断复位。

如下所示:

正常模块

C1(黄色:复位信号 XRSN)、C2(红色:GPIO17)、C3(蓝色:GPIO35)

异常模块

C1(黄色:复位信号 XRSN)、C2(红色:GPIO17)、C3(蓝色:GPIO35)

5.检查了内部时钟配置电阻器 R435。 其电阻值为正常值(1KΩ)、并且在没有冷焊接的情况下连接牢固。

摘要:

1.对于故障 MCU:回流焊后、3.3V 电源正常、内部时钟配置电阻 R435(1KΩ Ω)正常工作。 测试程序可以成功烧录、但 I/O 端口脉冲周期与编程设置不匹配。 当编程周期加倍时、I/O 端口周期保持不变、并且仍然与设置不匹配。

2.更换 MCU 恢复正常的模块性能,而重新安装原来的 MCU 重现异常。 这表示外设电路没有问题、并确认 MCU 本身存在功能异常。

根据上一份报告、还进行了其他实验。 内部时钟 (INTOSC1 和 INTOSC2) 和锁相环 (PLL) 系统时钟输出 (PLLSYSCLK) 通过 GPIO 输出。 一个示波器测量 10MHz 处 INTOSC1 和 INTOSC2 的频率、PLLSYSCLK 频率也保持在 10MHz。 修改 PLL 的倍频和分频配置参数后、PLLSYSCLK 频率仍保持为 10MHz 不变。

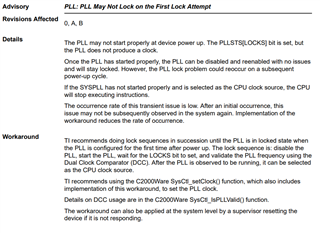

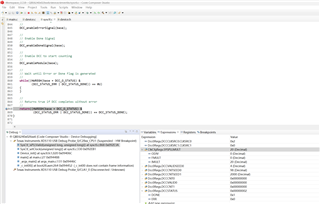

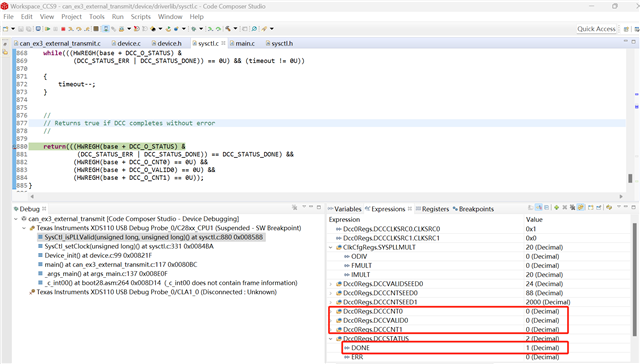

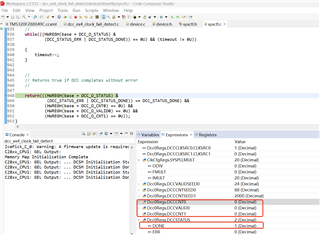

今天下午、进一步的问题定位测试表明、在故障模块的时钟初始化期间、PLL 有效性检查反馈始终指示故障。 请帮助确定在什么情况下可能发生此问题。