主题:C2000WARE 中讨论的其他器件

工具/软件:

您好、

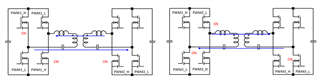

作为 CLLC 控制的一部分、为了在改变 PWM 相位时改变占空比、有必要输出下面的黄色波形。

在 E2E 工程师的最后一个回答中、我收到了以下评论。

——

您当然可以使用 CLB 来实现此目的。 最直接的方法是将周期性 PMW 信号路由到 CLB、以及第三个信号、该信号将与 PWM2_L 输出进行“或“运算、以根据需要延长输出的高电平时间。 第三个信号可以是使用 CLB 的 GPREG 输入的软件输入。 如果您在实施此方法方面需要帮助、请告诉我。

——

我正在考虑根据 E2E 工程师评论的内容专门实施 PWM 和 CLB、那么您能谈谈详细的方法吗?

谢谢、

Conor