工具/软件:

您好、

我试图了解 TIDM-DC-DC-BUCK 参考设计的时序、以便在我正在开发的设计中实现此目的。

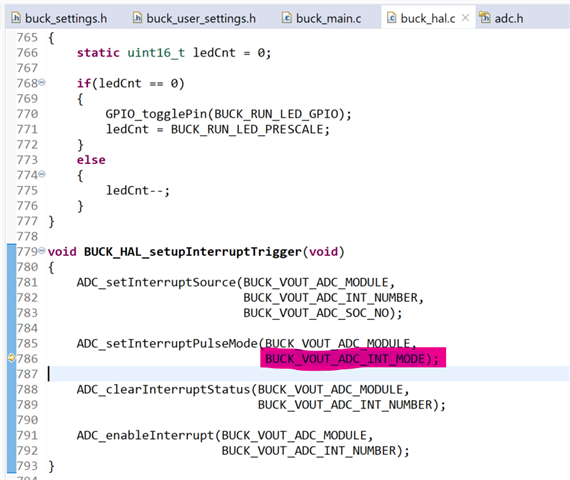

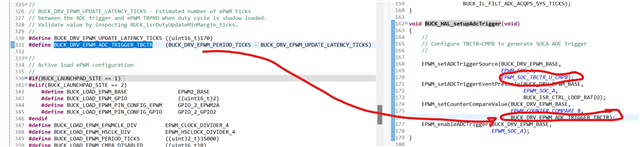

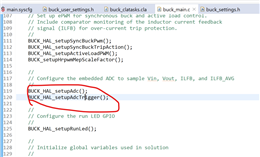

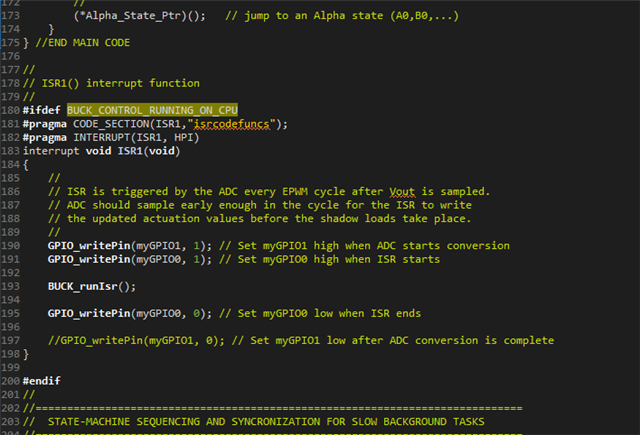

您是否知道是否可以输出与 ADC 时序相关的信号以进行探测? 还是 Code Composer Console 中的某个组件、可以显示用于计时的计数器? 我添加了一个 GPIO、以便在进入和退出 ISR 时变为高电平和低电平。 此外、我尝试添加一个 GPIO、当针对 SOC 触发 ADC 时、该 GPIO 会变为高电平、但在代码中找不到合适的位置来查看 ADC 何时开始转换和结束转换。 我还附上了添加 GPIO 的代码编辑版本。

e2e.ti.com/.../buck_5F00_F28004x.zip

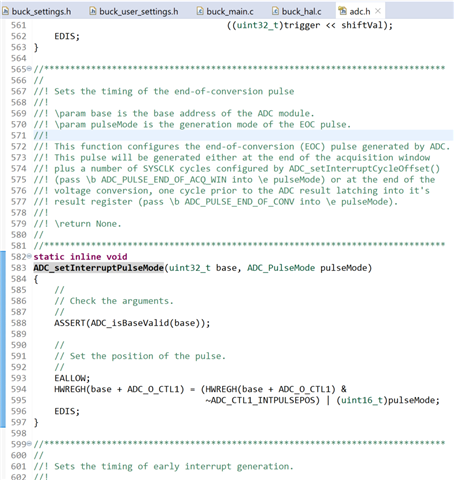

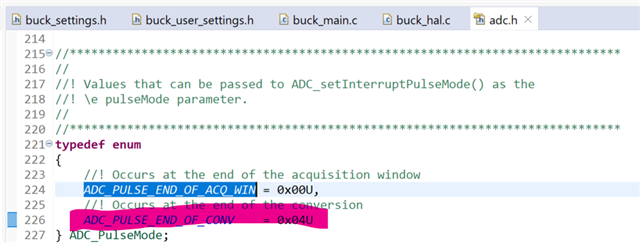

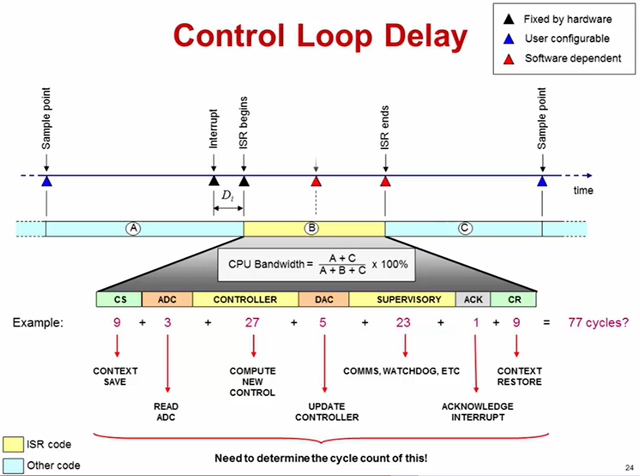

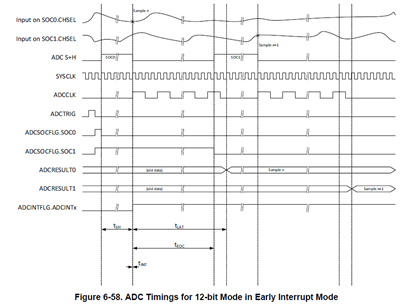

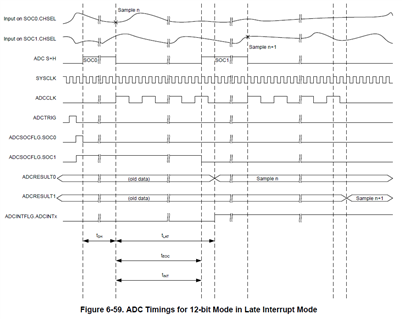

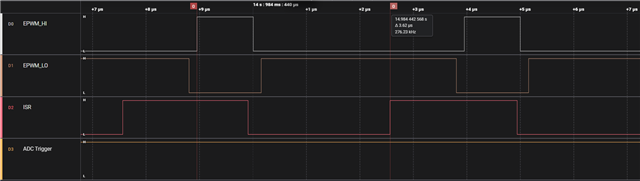

我粗略地绘制了一个时序图、说明了如何根据我在代码中阅读的内容了解循环应如何运行。 我让 ADC 由 ePWM 触发、然后 ADC 开始转换。 在 ADC SOC(采样保持和转换为数字)和 EOC 之间、根据 MCU 数据表和 ACQPS、我估计在触发 ADC 中断以启动降压 ISR 之前的延迟约为 280ns。 降压 ISR 延迟来自我使用 GPIO 测量的内容。 你觉得这有什么问题吗?

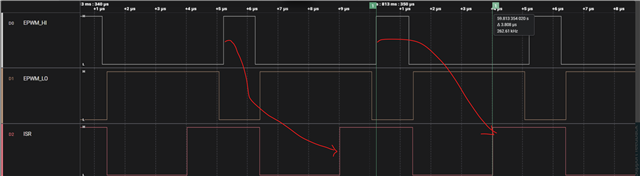

但是、在我探测 ISR 时、ePWM 延迟约为 3.62us。 此外、我查看了在点击“Resume un Code Composer(恢复代码编辑器)“后的工程启动情况、并注意到在 EPWM 开始切换之前 Buck_ISR 开始自行运行。 这可能是 ISR 和 ePWM 关闭同步的原因。 这让我感到困惑、因为我的印象是 ISR 依赖于 ADC 触发器、后者取决于 ePWM。 您对为什么会发生这种情况有任何见解吗? 是否应该发生这种情况?

降压启动

放大的降压启动

恭敬地说:

Mike Allette