工具/软件:

您好专家

客户在配电单元中使用我们的 F28377 时、发现 ADC 采样存在一些问题、如下图所示:

电源板上电时、蓝线/白线/黄线是不正确的 ADC 采样输出。

您可以看到这 3 条线路的下降和上升是相同的、这意味着相同的干扰信号可能耦合到 3 个通道。

绿色/红色/紫色线不会耦合干扰。

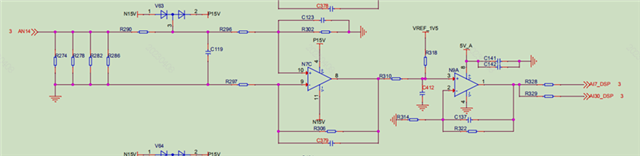

硬件连接如下:

蓝线 — AI13(x0.58)- ADCIND2/白线 — AI7(x0.14)- ADCINB4/黄线 — AI10(x1.4)- ADCINC2、典型输入电路:

MCU 原理图:

您有任何建议来调试此问题吗?

谢谢

Joe