Thread 中讨论的其他器件: TMS320F2800137、 C2000WARE

工具/软件:

尊敬的先生

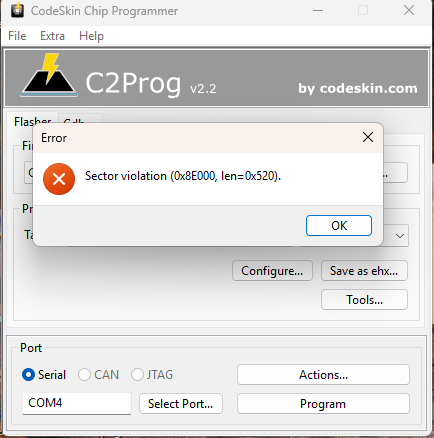

我采用了 LaunchPad TMS320F2800137 的示例程序 、将其目标更改为 TMS320F2800132 并进行编译、然后通过 C2prog 应用进行 SCI 引导加载 、但我收到扇区违例错误

请提供帮助

方面

Yusuf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的先生

我采用了 LaunchPad TMS320F2800137 的示例程序 、将其目标更改为 TMS320F2800132 并进行编译、然后通过 C2prog 应用进行 SCI 引导加载 、但我收到扇区违例错误

请提供帮助

方面

Yusuf

当我 在构建 F2800132_flash_lnk.cmd 文件时、我按照上述 方法使用 CCS 12.8.0。它显示存储器间隙错误闪存存储体的存储器地址与其长度和原点不正确对齐。 所以 我 根据长度定义更改 orgin 内存地址(附加更改的文件) 项目得到构建和生成.out 文件。 当我尝试使用 C2Prog 应用程序通过 SCI 引导加载程序加载.out 文件时,它显示出扇区违例 。 我认为在这个链接器文件中,内存分配有一些错误。

请给我发送闪存链接器文件

尊敬的 Yusuf:

0x8E000 地址位置指的是闪存组 0 扇区 56-63。 F2800132 器件只有 64KB 的可用闪存可用于编程、因此闪存编程不可用、超出 器件数据表中每个闪存映射的扇区 31 范围。

您是否可以参考 280013x_generic_flash_lnk.cmd 文件作为参考? 它位于以下位置:

C:\ti\C2000Ware_6_00_00\device_support\f280013x\common\cmd\280013x_generic_flash_lnk.cmd

错误原因可能是我们尝试对不可用的内存空间进行编程。

谢谢。此致、

Charles

尊敬的 Yusuf:

问题在于链接器文件对闪存编程使用的扇区超过 0-31(64KB 中分配的.text 扇区涵盖更大的范围) 。

我曾建议使用默认文件来比较它们如何设置扇区长度。

解决方法如下:

*

//###########################################################################

//

// FILE: F2800132_flash_lnk.cmd

//

// TITLE: Linker Command File For F2800132 Device

//

//###########################################################################

*/

MEMORY

{

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS0 : origin = 0x00008000, length = 0x00002000

RAMLS1 : origin = 0x0000A000, length = 0x00001FF8

// RAMLS1_RSVD : origin = 0x0000BFF8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RESET : origin = 0x003FFFC0, length = 0x00000002

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

GROUP { /* GROUP memory ranges for crc/checksum of entire flash */

#endif

#endif

BEGIN : origin = 0x00080000, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

/* Flash sectors */

FLASH_BANK0_SEC_0_7 : origin = 0x080002, length = 0x1FFE /* on-chip Flash */

FLASH_BANK0_SEC_8_15 : origin = 0x082000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_16_23 : origin = 0x084000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_24 : origin = 0x086000, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_25 : origin = 0x086400, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_26 : origin = 0x086800, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_27 : origin = 0x086C00, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_28 : origin = 0x087000, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_29 : origin = 0x087400, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_30 : origin = 0x087800, length = 0x0400 /* on-chip Flash */

FLASH_BANK0_SEC_31 : origin = 0x087C00, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_32 : origin = 0x088000, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_33 : origin = 0x088400, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_34 : origin = 0x088800, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_35 : origin = 0x088C00, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_36 : origin = 0x089000, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_37 : origin = 0x089400, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_38 : origin = 0x089800, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_39 : origin = 0x089C00, length = 0x0400 /* on-chip Flash */

//FLASH_BANK0_SEC_40_47 : origin = 0x08A000, length = 0x2000 /* on-chip Flash */

//FLASH_BANK0_SEC_48_55 : origin = 0x08C000, length = 0x2000 /* on-chip Flash */

//FLASH_BANK0_SEC_56_63 : origin = 0x08E000, length = 0x1FF0 /* on-chip Flash */

//FLASH_BANK0_SEC_63_DO_NOT_USE : origin = 0x08FFF0, length = 0x0010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

} crc(_ccs_flash_checksum, algorithm=C28_CHECKSUM_16)

#endif

#endif

}

SECTIONS

{

codestart : > BEGIN

.text : >> FLASH_BANK0_SEC_8_15 | FLASH_BANK0_SEC_16_23 | FLASH_BANK0_SEC_24 |

FLASH_BANK0_SEC_25 | FLASH_BANK0_SEC_26 | FLASH_BANK0_SEC_27 |

FLASH_BANK0_SEC_28 | FLASH_BANK0_SEC_29 | FLASH_BANK0_SEC_30 |

FLASH_BANK0_SEC_31 , ALIGN(8)

.cinit : > FLASH_BANK0_SEC_31, ALIGN(8)

.switch : > FLASH_BANK0_SEC_31, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

.bss : > RAMLS0

.bss:output : > RAMLS0

.init_array : >> FLASH_BANK0_SEC_31, ALIGN(8)

.const : >> FLASH_BANK0_SEC_31, ALIGN(8)

.data : > RAMLS0

.sysmem : > RAMLS0

.bss:cio : > RAMLS0

#else

.pinit : >> FLASH_BANK0_SEC_31, ALIGN(8)

.ebss : > RAMLS0

.econst : >> FLASH_BANK0_SEC_31, ALIGN(8)

.esysmem : > RAMLS0

.cio : > RAMLS0

#endif

#if defined(__TI_EABI__)

.TI.ramfunc : LOAD = FLASH_BANK0_SEC_8_15,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : LOAD = FLASH_BANK0_SEC_8_15,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

/* Allocate IQ math areas: */

IQmath : > RAMLS1

IQmathTables : > RAMLS1

/* crc/checksum section configured as COPY section to avoid including in executable */

.TI.memcrc : type = COPY

}

/*

//###########################################################################

// End of file.

//###########################################################################

*/

谢谢。此致、

Charles

谢谢 Charles 问题得到解决 、通用链接器文件中存在问题 const 和 cinit 尝试加载到 F2800132 中不存在的扇区 32_39 上 。我按如下所示更改了链接器文件并成功更改了

MEMORY

{

BEGIN : origin = 0x00080000, length = 0x00000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS0 : origin = 0x00008000, length = 0x00002000

RAMLS1 : origin = 0x0000A000, length = 0x00001FF8

// RAMLS1_RSVD : origin = 0x0000BFF8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

FLASH_BANK0_SEC_0_7 : origin = 0x080002, length = 0x1FFE /* on-chip Flash */

FLASH_BANK0_SEC_8_15 : origin = 0x082000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_16_23 : origin = 0x084000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_24_31 : origin = 0x086000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_32_39 : origin = 0x088000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_40_47 : origin = 0x08A000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_48_55 : origin = 0x08C000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_56_63 : origin = 0x08E000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_64_71 : origin = 0x090000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_72_79 : origin = 0x092000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_80_87 : origin = 0x094000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_88_95 : origin = 0x096000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_96_103 : origin = 0x098000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_104_111 : origin = 0x09A000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_112_119 : origin = 0x09C000, length = 0x2000 /* on-chip Flash */

FLASH_BANK0_SEC_120_127 : origin = 0x09E000, length = 0x1FF0 /* on-chip Flash */

// FLASH_BANK0_SEC_127_RSVD : origin = 0x09FFF0, length = 0x0010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

codestart : > BEGIN

.text : >> FLASH_BANK0_SEC_8_15 | FLASH_BANK0_SEC_16_23 | FLASH_BANK0_SEC_24_31 , ALIGN(8)

.cinit : > FLASH_BANK0_SEC_0_7, ALIGN(8)

.switch : > FLASH_BANK0_SEC_0_7, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

.bss : > RAMLS0

.bss:output : > RAMLS0

.init_array : >> FLASH_BANK0_SEC_0_7, ALIGN(8)

.const : >> FLASH_BANK0_SEC_24_31, ALIGN(8)

.data : > RAMLS0

.sysmem : > RAMLS0

.bss:cio : > RAMLS0

#else

.pinit : >> FLASH_BANK0_SEC_0_7, ALIGN(8)

.ebss : > RAMLS0

.econst : >> FLASH_BANK0_SEC_24_31, ALIGN(8)

.esysmem : > RAMLS0

.cio : > RAMLS0

#endif

#if defined(__TI_EABI__)

.TI.ramfunc : LOAD = FLASH_BANK0_SEC_0_7,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : LOAD = FLASH_BANK0_SEC_0_7,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

/* Allocate IQ math areas: */

IQmath : > FLASH_BANK0_SEC_24_31, ALIGN(8)

IQmathTables : > FLASH_BANK0_SEC_24_31, ALIGN(8)

}