主题中讨论的其他器件: TMS320F280049C、TMS320F280049-Q1

工具/软件:

您好支持、

我们基于 280049 微控制器开发了一个机载应用程序、其驱动程序主要源自 C2000ware 版本 4.3、用于时钟/PLL 设置和控制 (sysctl.c)

今天、在查看我们的代码并将其与最新版本的 C2000ware (5.05) 和最新版本的 TRM 进行比较时、我们注意到某些时序和重试次数已经被修改

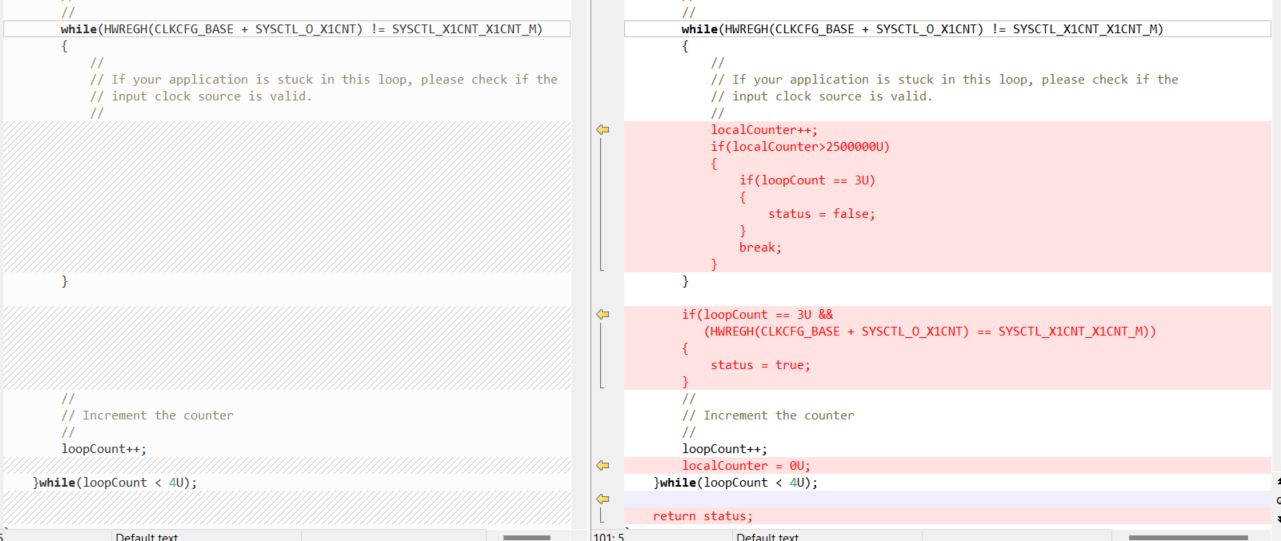

1) 等待 X1 时钟饱和时

添加了退出循环的超时选项:

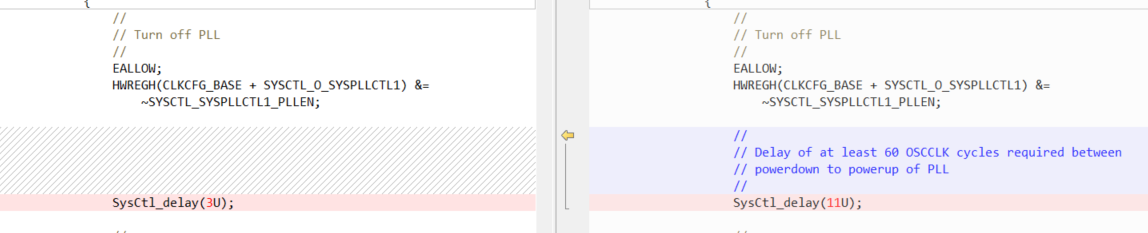

2) 关闭 PLL 时

添加了从 断电到 PLL 上电之间至少需要 60 个 OSCCLK 周期的延迟

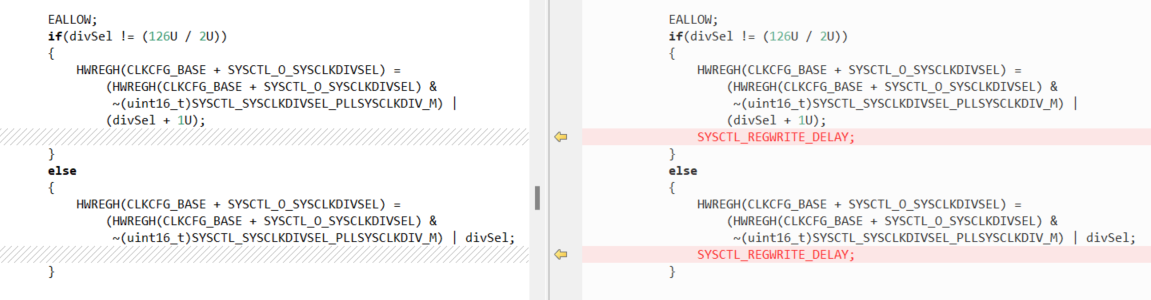

3) 在 SYSCTL_O_SYSCLKDIVSET/SYSCTL_O_XTALCR/SYSCTL_O_CLKSRCCTL1 寄存器中写入分频器时

增加了延迟

SYSCTL_REGWRITE_DELAY、即 asm(“ RPT #39 || NOP“)

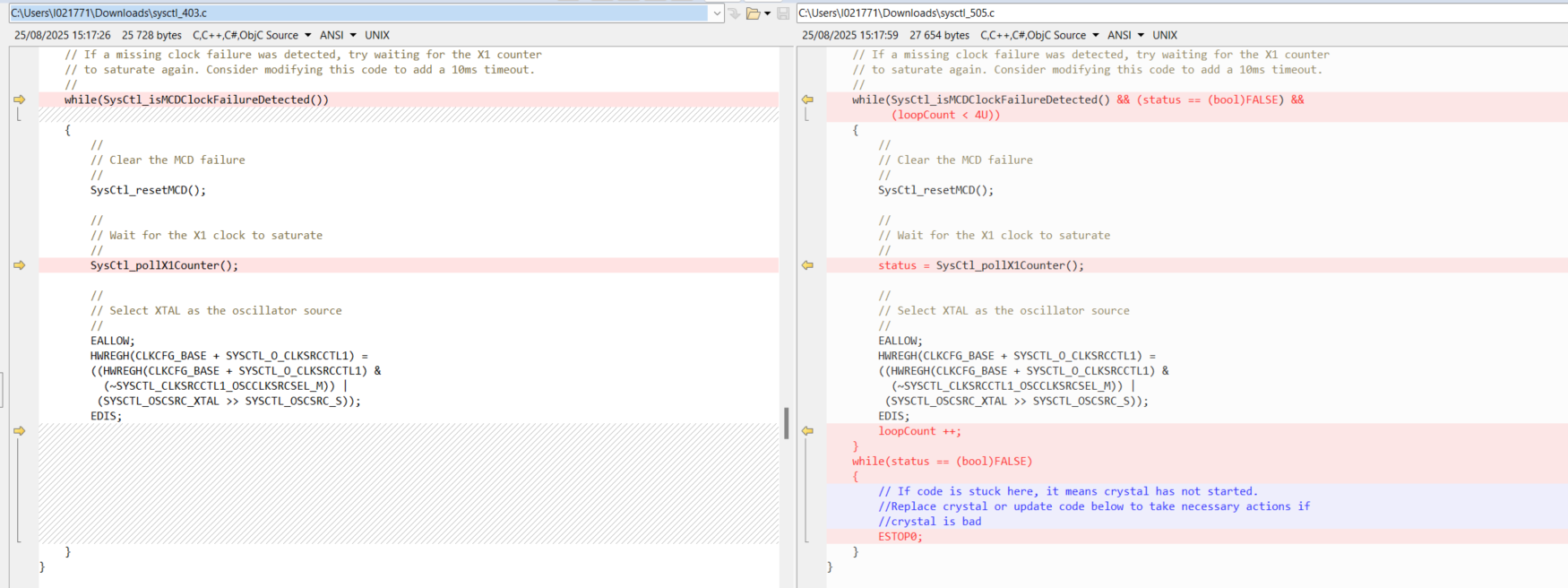

4) 检查丢失时钟故障时

添加了一个计数器选项以退出循环、并停止程序执行

我们能否生活在没有这些变化的情况下,或者它们真的必须 在我们的代码中实现?

我们目前正处于修改我们的代码的阶段、我们需要重新运行所有高级测试并重放一些低级测试。

提前感谢您。

David