工具/软件:

您好:

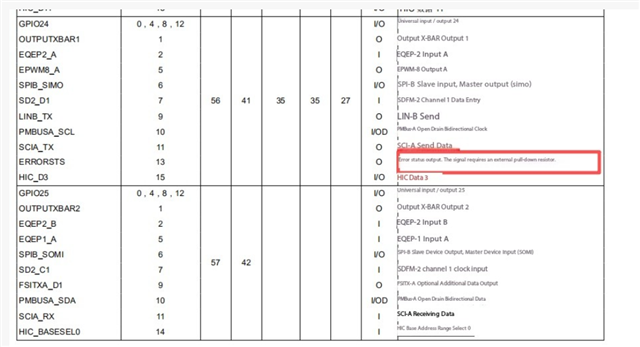

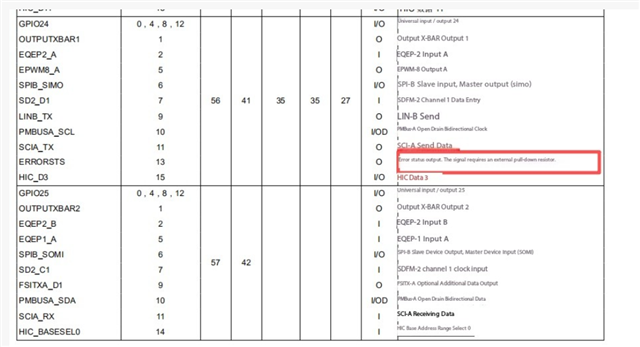

这里存在一种现象、当 GPIO25 在下拉状态下上电时、芯片无法引导、但在上拉状态下、芯片可以引导。 这是否与 GPIO24 相关? 上图指示:错误状态输出。 该信号需要一个外部下拉电阻器。请让专家帮助回答这个问题、谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

这里存在一种现象、当 GPIO25 在下拉状态下上电时、芯片无法引导、但在上拉状态下、芯片可以引导。 这是否与 GPIO24 相关? 上图指示:错误状态输出。 该信号需要一个外部下拉电阻器。请让专家帮助回答这个问题、谢谢!

您好、Tony、

复位后、默认引导模式引脚为 GPIO24 和 GPIO32(不是 GPIO25)。 如果两者都= 1、则器件引导至闪存。 任何其他组合都会选择其他模式 (CAN/SCI/WAIT)、这可能看起来像“无引导“。 请确保您的电路板自举在上电/复位时放置 GPIO24=1 和 GPIO32=1。

GPIO25 不是引导选择引脚。 如果将其下拉会阻止引导、则通常表示下拉网络或连接的电路正在加载或耦合到引导引脚 (GPIO24/32) 中、或者在采样窗口期间将一些其他关键信号(例如,复位/NMI 域)保持在错误状态。 在 XRSn 释放时测量 GPIO24 和 GPIO32 的实际逻辑电平;其中一个可能被拉低。

关于 ERRORSTS 信号(器件“错误状态“输出)、它是一个输出、可以路由到一组特定的 GPIO。 它不应由外部逻辑驱动。 如果在您的设计中实现为开漏/低电平有效型输出、它通常使用上拉电阻、因此器件可以将其拉至低电平以发出错误信号。 仔细检查器件/电路板的确切引脚映射和偏置;请勿使用具有强下拉电阻的自举网络、该强下拉电阻可能会在复位时与输出驱动器或反向电源引脚战斗。

此致、

Masoud