实际上、我让它可以完成这个过程。 我将两个 CPU 的 cmd 文件更改为具有从 0x103xxxxx 开始的 CPU3 的所有闪存地址。 我尝试了上述过程、但它未能在步骤 4 中写入 CPU 3 的 0x1030000 闪存空间。 改回原来的,现在闪烁的作品,甚至适应我们自己的双核作品。 真的很好奇这里可能发生了什么? 此外、我还在寻找一个存储器映射、该存储器映射详细说明了 SRAM/闪存的默认映射、但无法找到任何内容。 有什么存在吗?

就像电路板有一些需要写入或复位的问题一样吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

实际上、我让它可以完成这个过程。 我将两个 CPU 的 cmd 文件更改为具有从 0x103xxxxx 开始的 CPU3 的所有闪存地址。 我尝试了上述过程、但它未能在步骤 4 中写入 CPU 3 的 0x1030000 闪存空间。 改回原来的,现在闪烁的作品,甚至适应我们自己的双核作品。 真的很好奇这里可能发生了什么? 此外、我还在寻找一个存储器映射、该存储器映射详细说明了 SRAM/闪存的默认映射、但无法找到任何内容。 有什么存在吗?

就像电路板有一些需要写入或复位的问题一样吗?

Simon、

我现在就可以使用这个过程了。 我将两个 CPU 的 cmd 文件更改为具有从 0x103xxxxx 开始的 CPU3 的所有闪存地址。 我尝试了上述过程、但在步骤 4 中未能写入 CPU 3 的 0x1030000 闪存空间。

我不确定您的意思、但代码开头+ CERT 在闪存开头有固定的位置。

改回原来的,现在是盲目的作品,甚至是我们自己的双核作品的改编。 [/报价]您是否在两次运行之间进行了 POR? 因为这也可以代替 XRSN、因为它是器件级复位。

还一直在寻找一个内存映射、该映射详细说明了 SRAM/闪存的默认映射、但无法找到任何内容。 有什么存在吗?您能详细说明一下您的意思吗? 我们在 RAM/闪存地址的器件数据表中有存储器映射。 我们还在数据表和 TRM 中提供了基于 BANKMODE 的闪存映射。 请注意、CPU2 无法访问闪存。

主板几乎有一些问题需要写入或重置?除了与复位有关之外、这似乎不是电路板问题。

此致、

Aishwarya

[/quote]

感谢您的答复、我不记得我是否执行了 POR。 我只能说、以前的过程失败了、现在相同的序列也起作用了。 我不明白为什么。

就我要寻找的存储器映射而言、我想了解每个处理器在哪里可以看到不同的 SRAM 和闪存部分、以便我可以挑选一些特定部分来共享数据。 我现在可以使其在 SRAM 的 CPU1 和 CPU3 之间正常工作、并共用 CDA0 的一个部分。 但是、CPU3 的闪存区域定义在地址 0x10400000 处、当 CPU1 闪存从 0x10000000 开始时、该地址看起来在程序/数据闪存的 MAIN 4MB 之后。 我基本上尝试将 CPU3 闪存区域移动到 0x10300000、但它不起作用、但我不明白为什么?

可访问的 SRAM 段似乎从 0x200E0000 开始、从 0x10000000 开始闪存是正确的、在哪里可以找到完整的映射?

Simon、

我分开了话题、因为这个问题与我们最初讨论的问题有点不同。 此处链接的主题: F29H850TU:多核调试 — C2000 微控制器论坛。

我想不到其他硬件设置可能是修复的原因。 如果您想了解其他信息、请告诉我。

[引述 userid=“671670" url="“ url="~“~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1570747/re-f29h850tu-multicore-debugging/6048137就我要寻找的存储器映射而言、我想了解每个处理器在哪里可以看到不同的 SRAM 和闪存部分、以便我可以挑选一些特定部分来共享数据。 我现在可以使其在 SRAM 的 CPU1 和 CPU3 之间正常工作、并共用 CDA0 的一个部分。 但是、CPU3 的闪存区域定义在地址 0x10400000 处、当 CPU1 闪存从 0x10000000 开始时、该地址看起来在程序/数据闪存的 MAIN 4MB 之后。 我基本上尝试将 CPU3 闪存区域移动到 0x10300000、但它不起作用、但我不明白为什么?

可访问的 SRAM 段似乎从 0x200E0000 开始、从 0x10000000 开始闪存是正确的、在哪里可以找到完整的映射?

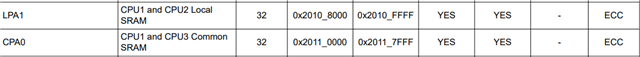

[/报价]与任何其他外设一样、SRAM 和闪存是具有起始/结束地址的存储器映射。 无论是 CPU1 还是 CPU2 访问 SRAM、它们都将使用相同的地址。 假设这也是您的理解。 例如、所有三个 CPU 都可以访问 LPA1 和 CPA0。 不过、LPAx 针对 CPU1 和 CPU2 访问进行了优化、而 CPAx 针对 CPU1 和 CPU3 访问进行了优化。 LDAx 和 CDAx 的概念相同。

(数据表中存储器映射部分的片段)

(数据表中存储器映射部分的片段)

如果您查看任何闪存构建示例、您将看到 CPU1 CERT @ 0x10000000、 CPU1 codestart @ 0x10001000 、CPU3 CERT @0x10400000、 CPU3 codestart @0x10401000。 与 CPU1 类似、存在一个固定的 CPU3 codestart 和 CERT 位置。

要在刷写无效的 codestart 程序后对闪存重新编程、您可以将引导模式从 11(闪存引导)更改为 00、执行 CPU 复位或下电上电、重新连接以及刷写有效代码启动程序。

此致、

Aishwarya