Other Parts Discussed in Thread: TMS320F280025

工具/软件:

您好:

我正在处理 TMS320F280025 微控制器、C2000 v5.0.00.00 和安全诊断库 v4.01.00 的项目。

该系统基于两个中断:

- Timer2(500ms 周期):在 ISR 内、CPUTIMER_TCR_TIF 根据线程中的需要清除:

TMS320F280025:HWBIST 测试后的虚假中断 - ADC(具有 55µs 周期):每次发生 ISR 时、都会执行 STL_HWBIST_runMicro、直到 HWBIST 测试完成。 之后、闪存 ECC 测试将执行一定数量的周期、以运行可纠正和不可纠正的测试…μ s 然后、该循环从 HWBIST 测试重新启动。

- 没有其他中断干扰正常运行、系统会正确调度。

我注意到、有时 timer2_ISR 的执行延迟的时间等于执行闪存测试的 ADC_ISR 周期数。 之后、STL_HWBIST_runMicro 的执行似乎会恢复正常操作。

这一问题似乎不会在两种不同的情况下发生、即:

- CPUTIMER_TCR_TIF 不能由 timer2_ISR 清除(因此不能通过 HWBIST 测试清除、因为这意味着虚假计时器 2 中断)。

- 与 IER、PIEIER12 和 EINT/DINT 相关的指令不会在 ADC_ISR 的 else 语句中执行。

提前感谢您的支持。

以下是代码:

__ interrupt void timer2_isr (void)

{

//一些代码...

//清除溢出标志—这是避免虚假中断的强制性操作

//在 HWBIST 微运行执行之后。

CPUTimer_clearOverflowFlag (CPUTIMER2_BASE);

}

中断无效 ADC_ISR (void)

{

//一些代码...

//确认中断组 1 以允许来自该组的进一步中断

INTERRUPT_CLEARACKGROUP (INTERRUPT_ACK_GROUP1);

if(条件==1)

{

//一些代码...

//执行 HWBIST 微运行

STL_HWBIST_runMicro ();

//一些代码...

}

暴露

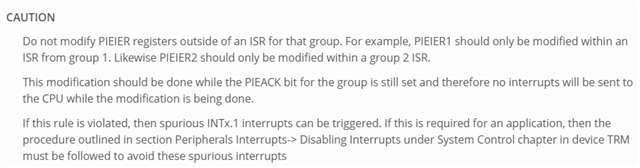

{

Uint16_t PIEIER_prev = HWREGH (PIECTRL_BASE + PIE_O_IER12);

// IER:禁用除组 12 和 ERAD 之外的所有中断。

IER &= INTERRUPT_CPU_INT12 | INTERRUPT_CPU_RTOSINT;

// PIEIER12:禁用组 12 的所有中断

//除了闪存可纠正的错误中断。

HWREGH (PIECTRL_BASE + PIE_O_IER12)&= PIE_IER12_INTX11;

//启用中断。

EINT;

//执行闪光自检。

flash_selfest ();

//禁用中断。

DINT;

//恢复中断寄存器。

HWREGH (PIECTRL_BASE + PIE_O_IER12)= PIEIER_PREV;

}

}