器件型号: TMS320F28P650SH

尊敬的 Champs:

现在、我的客户对 CLB CLK 有了一些疑问。

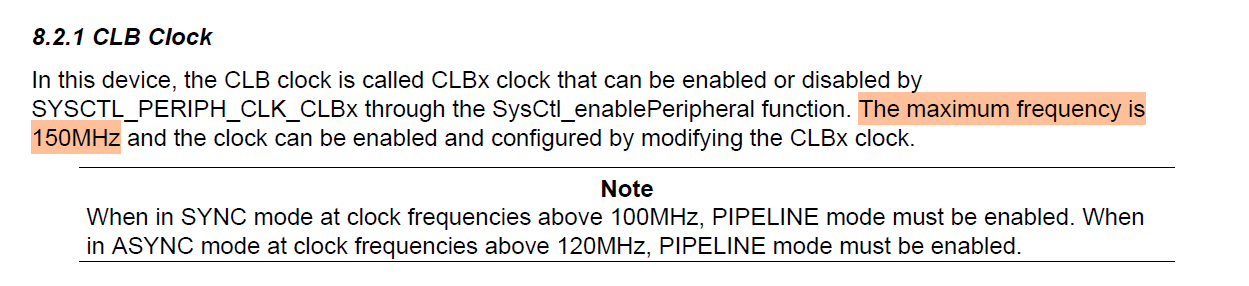

- TRM 显示 CLB 最大频率为 150MHz 。 这是否意味着最大 CLB 寄存器时钟和最大 CLB 逻辑块时钟都是 150MHz?

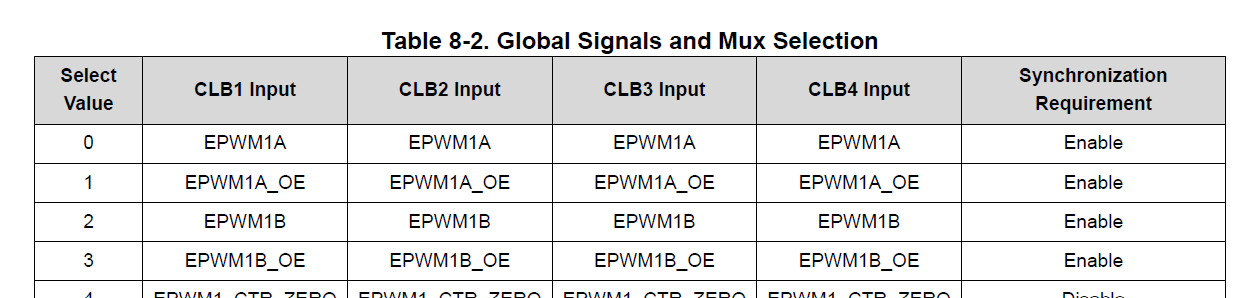

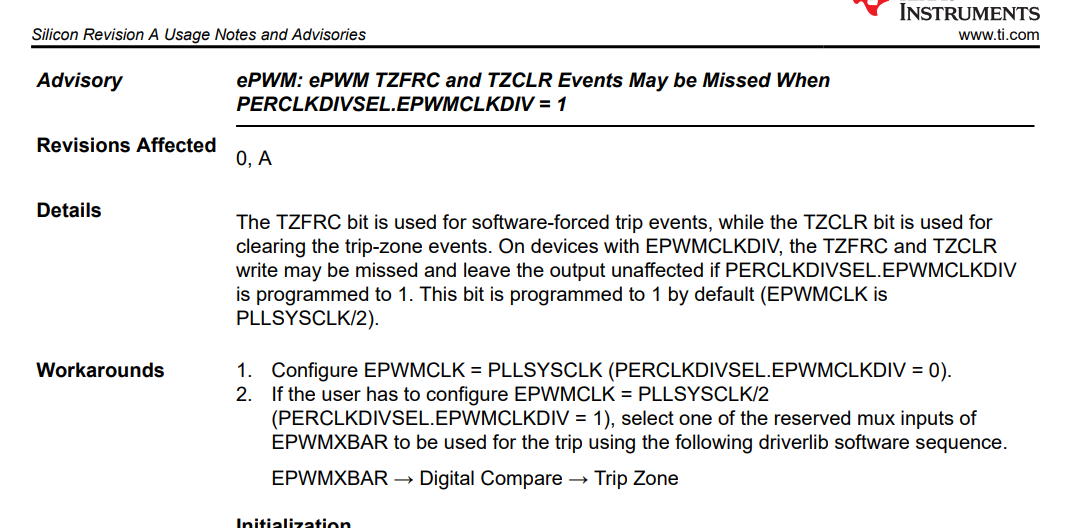

2.如果客户使用 EPWM 作为 CLB 输入、则需要同步。 但是、当 EPWMCLKDIV 进行 2 分频时、EPWM TZFRC 和 TZCLR 事件有时会丢失、因此我们需要将 EPWMCLK 设置为 200MHz。 如果需要在同步模式下运行、CLB 逻辑块和寄存器时钟将与 200MHz EPWMCLK 同步。 这似乎无法满足 CLB CLK 的要求。 我们如何解决这个问题? 我们是否可以使用 200MHz CLB 寄存器时钟和 100MHz 逻辑块时钟?

谢谢!

此致、

Julia