Other Parts Discussed in Thread: SYSCONFIG

器件型号: TMS320F28386D-Q1

主题: SysConfig 中讨论的其他器件

您好:

我的问题与 FSI Rx 内核发出的硬件信号有关。

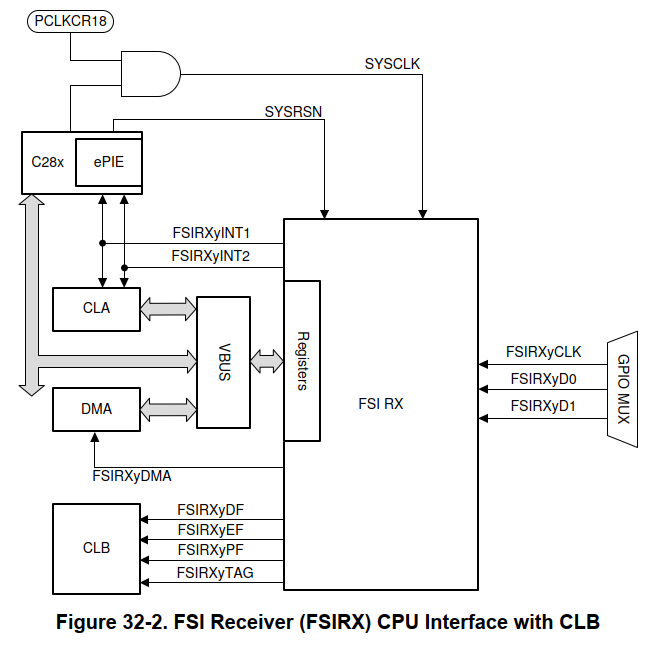

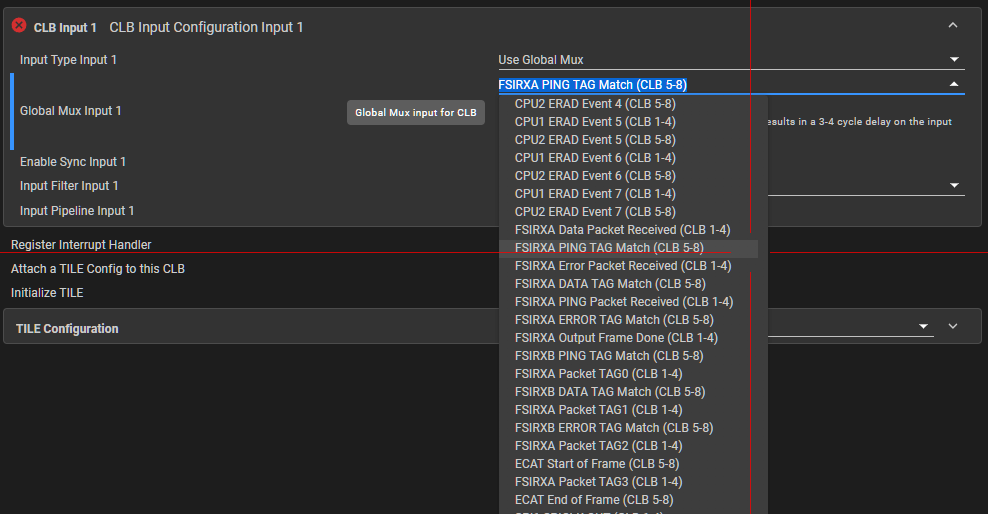

从 相关 TRM 的第一个摘录图 32-2 中、我们观察到 FSI Rx 内核发出四个信号。 从第二个屏幕截图(CLB SysConfig 工具)以及 TRM 的表 9-2 中、我们观察到可以选择几个其他 FSI 相关信号(例如“FSIRXA Ping Tag Match“)作为 CLB 的输入源。

虽然遗憾的是、TRM 中没有说明这一切、但可以推断、可供 Rx 输入使用的 FSI-CLB 相关信号总数可能是 FSI Rx 内核发出的四个“内核“信号集的逻辑组合、如图 32-2 所示。 例如、“FSIRXA Ping 标记匹配“实际上是图 32-2 中所述的“FSIRXPF"和“和“FSIRXTAG"信号“信号的逻辑交叉点(和)、其中假设中的“FSIRXTAG"解释“解释为表示标签匹配的逻辑信号。

作为一阶、 请确认(或以其他方式更正)此假定行为。

一个后续问题是、这些大概是每个 FSI Rx 内核各自的逻辑组合信号、这些信号作为在通用时钟域中计时的 CLB 输入提供并进行时间协调、以便我可以针对来自给定 FSI Rx 内核的多个此类信号安全地在 CLB 中执行组合逻辑吗?

一个具体的示例是、如果我将“FSIRXA Ping Tag Match“指定为分配给输入 0 的 CLB 输入(我们将其中表示 i0)、将“FSIRXA Ping Packet Received“指定为 CLB 输入 1 (i1)。 假设每个输入具有相同的输入同步器设置、我是否可以安全(期望无干扰操作)构建一个执行 i0 &!i1 的 LUT、以生成一个有效的信号、即“FSIRXA Ping 帧、无标签匹配“? 或者这是否会潜在的干扰、从而需要一些更高阶的逻辑电路?

表 9-2 中概述的“FSIRXA_PKT_TAG0/1/2/3"的“的含义是什么? FSI Rx 内核没有多个标签匹配寄存器。

提前感谢、

David Michaud