器件型号: TMS320F28388D

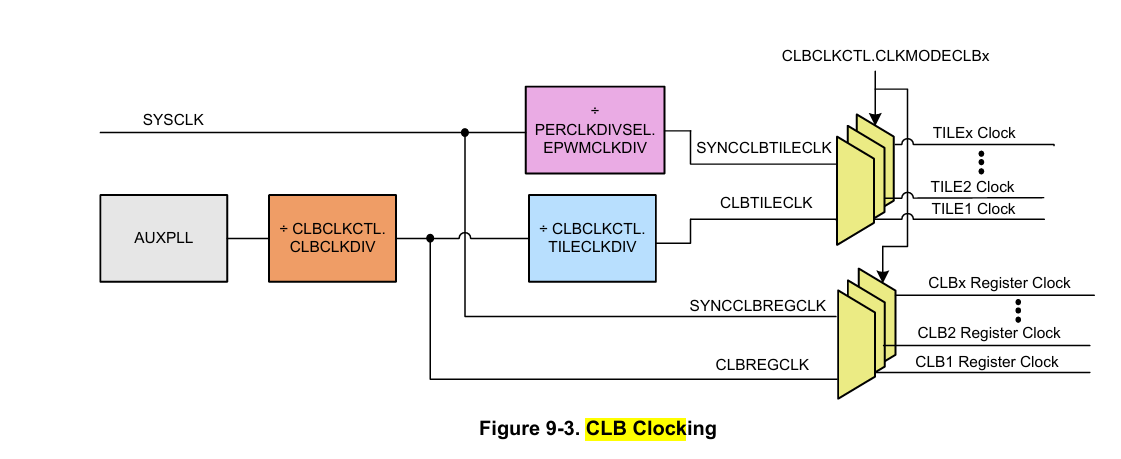

您好、我参考了 f28388D TRM、因为根据下图所示的 TRM CLB 时钟配置。

如图所示、这里有两个输入 1) AUXPLL 2) SYSCLK

1) 需要配置哪个寄存器来定义来自上述两个源的时钟输入。

2) 而在 TRM 中 、它显示 2 个可能的输入、而在 syscfg 中、它仅显示 AUXPLL 作为输入

3) 通过启用 SYNC(通过 CLKMODECLB1 ),它可以确保与 SYSCLK 相位对齐,或者根据禁用 SYNC 的情况来确保一些额外的功能。

此致