器件型号: TMS320F28P550SG

您好、TI 专家、

当使用 100 引脚 P55 MCU 并选择 VDDA 3V 作为 ADC 基准电压时、是否可以同时使用两个 VREFLO 引脚 (26 和 27) 进行模拟输入采样?

此外、如果选择了两个 VREFLO 引脚 (26/27) 中的一个和两个 VREFHI 引脚 (24/25) 中的一个、那么 它们是否可以配置为模拟输入通道进行采样?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: TMS320F28P550SG

您好、TI 专家、

当使用 100 引脚 P55 MCU 并选择 VDDA 3V 作为 ADC 基准电压时、是否可以同时使用两个 VREFLO 引脚 (26 和 27) 进行模拟输入采样?

此外、如果选择了两个 VREFLO 引脚 (26/27) 中的一个和两个 VREFHI 引脚 (24/25) 中的一个、那么 它们是否可以配置为模拟输入通道进行采样?

尊敬的 Jianjun:

这些引脚不会释放您可以独立使用的额外通道;它们是共享的、并且在选择 VDDA/VSSA 时会发出耦合公告。 如果所有 ADC 都使用 VDDA/VSSA 基准、则可以根据模拟引脚说明将 VREFHI/VREFLO 引脚用作 ADC 输入通道。

也就是说、当 ADC 基准设置为 VDDA/VSSA 时、VREFHI 和 VREFLO 与某些 ADC 通道共享、并且在该模式下、VREFHI 和 VREFLO 引脚之间也存在电阻连接。 由于该电阻连接、我们建议采用权变措施:如果将其用作模拟输入、则仅驱动这两者中的一个、并使另一个保持悬空。 如果将这些引脚用作 ADC 输入、则只能驱动其中一个引脚并使另一个引脚悬空。

此致、

Masoud

尊敬的 Masoud:

感谢您的答复。 我还有两个问题。

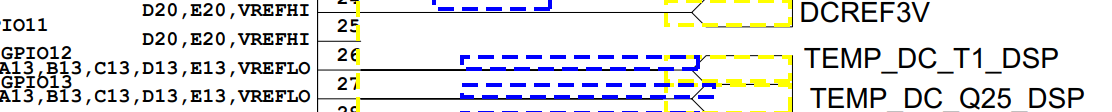

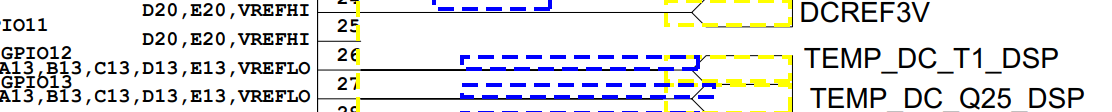

当 VREFHI 和 VREFLO 引脚)模拟基准时< 1 μ s。 两个高基准信号引脚 VREFHI (24) 和 VREFHI (25) 中的一个是否可以连接到 DCREF3V、同时让另一个引脚悬空? 两个 VREFLO (引脚 26/27)都连接到 DSP_GND?

当 VREFHI 和 VREFLO 引脚)模拟基准时小于 2 μ s。 100 引脚 P55 VREFHI (24/25) 和 VREFLO (26.27) 的标准连接方法是什么? 谢谢你。

![]()

尊敬的 Jianjun:

如果 VREFHI/VREFLO 用作 ADC 基准(外部基准模式)、 VREFHI 引脚 24 和 25 必须在 PCB 上连接在一起、并且两者都应连接到同一个外部基准源。 同样、VREFLO 引脚 26 和 27 必须连接在一起、并且应连接到同一个低基准节点 (VSSA/模拟 GND)。

此外、将所需的电容器放置在 VREFHI 和 VREFLO 之间、尽可能靠近器件。

如果选择 VDDA/VSSA 作为 ADC 基准(模拟电源作为基准)、则在该模式下、VREFHI 和 VREFLO 引脚不是自由独立的通道;它们与 ADC 输入共享(VREFHI 与 D20/E20 共享、VREFLO 与 A13/B13/C13/D13/E13 共享)。 如果您选择在此模式下将共享引脚用作 ADC 输入、请注意勘误表公告:共享模拟输入之间可能有一个电阻路径。 建议的权变措施是仅驱动其中一个重复的引脚、将另一个引脚用作模拟输入时、使其保持悬空。

此致、

Masoud