“线程:sysconfig, test, LAUNCHXL-F280025C”中讨论的其它部分

你(们)好

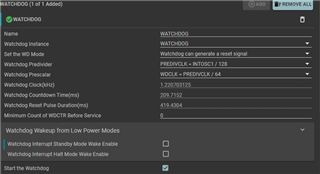

我已设置看门狗在209 ms 后触发。

到目前为止,我没有设置看门狗的任何服务,所以它应该重新设置我的设备,或者拔下插头。

事实上,在首次启动后,它会重置设备,并持续一段时间,但随后它会停止执行此操作。

首先,我认为设备卡在某些 NMI 中,或者存在某些异常。 但事实证明,它运行正常,我的应用程序代码运行时就好像没有看门狗一样。

简而言之

预测:

设备每隔209毫秒重置一次,直到断电。

现实:

设备在一段时间内每209 MS 重置一次,然后重置事件停止,CPU 运行正常的软件。

“一些时间”=可变时间大约为2秒到20秒。

使用 sysconfig 工具设置看门狗:

随着209 MS 运行时间的推移,有足够的时间在串行端口上打印一些调试信息。

所以我在串行初始化后添加了这一项

Log_debug("WatchDog counter value = %u\r\n", SysCtl_getWatchdogCounterValue());

Log_debug("WatchDog reset status = %d\r\n", SysCtl_getWatchdogResetStatus());

Log_debug("Sys control and status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_SCSR));

Log_debug("WatchDog KEY register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDKEY));

Log_debug("WatchDog status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDCR));

Log_debug("WatchDog Windowed status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDWCR));

* Log_debug 只是将宏扩展到 printf

我明白了

DBG: WatchDog counter value = 1 DBG: WatchDog reset status = 0 DBG: Sys control and status register = 5 DBG: WatchDog KEY register = 7 DBG: WatchDog status register = E07 DBG: WatchDog Windowed status register = 0

当 以后触发重置时,这两个值都相同。

我的 testmonitor 中还有这些值在命令上打印,当我要求它们在重置停止后,我仍然得到相同的值,除了不断变化的计数器(表示它正在运行)

那么,为什么我的看门狗停止工作?