在“线程:sysconfig, C2000WARE,LAUNCXL-F280025C”中讨论的其他部件

背景:尝试使用 输出 LUT 块插入三个脉冲(从外部硬件到三个 GPIO)的查找表功能:CLB 模块,输出需要在 ECAP 中使用。 因此,我需要先查看输出 LUT 块到 GPIO 的输出信号,以使用示波器查看其性质,然后连接到 ECAP1。 在经历“云杉7a”的过程中,许多地方感到困惑。

1. 我使用以下代码:

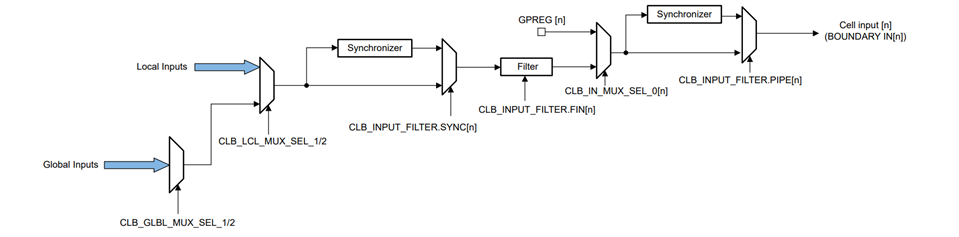

CLB 输入 X-bar 用作三个 GPIO 的输入,如下所示:

ClbInputXbarRegs.INPUT1SELECT=11;//作为 CLB 输入的 GPIO11

ClbInputXbarRegs.INPUT1SELECT=27;//作为 CLB 输入的 GPIO27

ClbInputXbarRegs.INPUT1SELECT=42;//作为 CLB 输入的 GPIO42

因此,CLB 输入 X 条信号可以进入输出 LUT 块的输入:页码1279 (图12-14)中的 CLB 模块。

2.第1271页,表12-4将8个“外部信号”23至31定义为输出 LUT 块的输入:CLB 模块。 但是,混淆了:哪些信号构成了这些外部信号?

3.如何将这8个数字的“外部信号”连接到第1265页图12-5中 CLB 输入 X-bar 输出的 Input1-INPUT16信号。

4.让我知道我需要为自己的目的配置哪些关联的寄存器?