您好,champs:

我的客户有以下CAN模块问题,

- 当CAN模块面临位错误问题时,能否获得详细的数据包内容信息?

- 当采样点在边缘后面且计时器间隔小于1次量子时,此采样计时是否会导致位误差?

如果有,请提出您的想法,感谢您的帮助。

此致,

卢克

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,champs:

我的客户有以下CAN模块问题,

如果有,请提出您的想法,感谢您的帮助。

此致,

卢克

Hareesh您好

我是Luke的客户。 感谢你的帮助。

我们面临的问题是CAN模块出现许多"表单错误"并进入总线关闭状态。

我们使用“错误帧”来查找哪一位触发器格式错误。

我们发现这是"ACK定界符"。

接下来,我们要查找导致表单错误的原因。

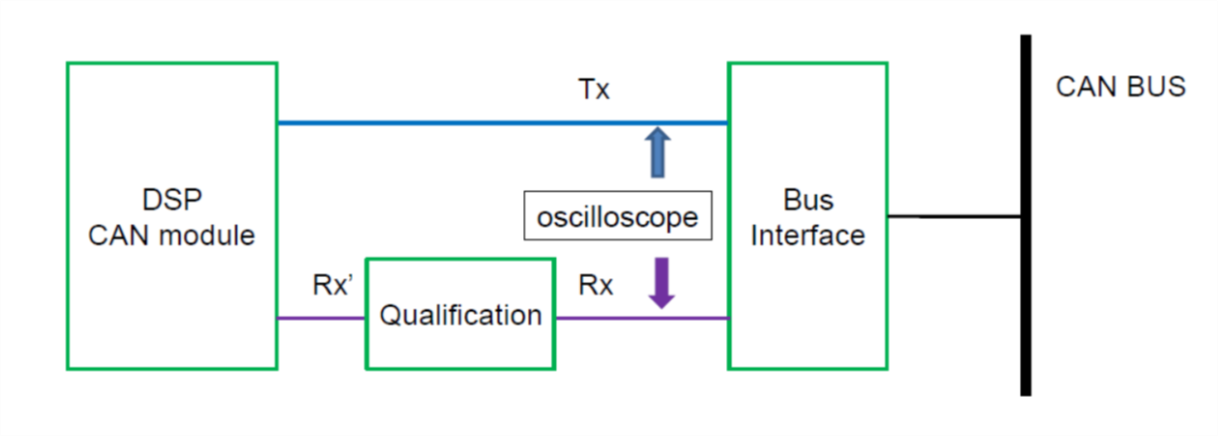

我们测量Tx (蓝色),Rx (紫色)的波形。 位定时的波形和派生如下所示。

Rx和Rx'之间的时间延迟来自GPIO的输入鉴定。

我们假设时间延迟为0.167us(最坏的情况)。

一位时间为1us,我们在一位时间内以0.8us的值进行采样。

通过派生,我们发现ACK定界器的采样点位于上升边缘后面。

时间差约为0.04us,小于1 TQ (0.067us)。

在ACK定界符处发生表单错误,这意味着CAN模块应在ACK定界符处采样“0”。

但通过派生位计时,我们得到的结果是ACK分界符的采样点在上升边缘后面,模块应在ACK分界符处对“1”进行采样。

我们的位计时派生是否错误?

或者,当采样点和边缘之间的时间差小于1 TQ时,CAN模块采样值可能不正确吗?

我们已经运行了一个实验,删除了GPIO的输入限定,并且不会出现格式错误。

谢谢!

魏清伟

程

输入鉴定具有延迟设备内部信号的效果。 头文件中清楚地显示了这一点:

//将选定CAN引脚的限定条件设置为仅同步

//默认情况下,输入与SYSCLKOUT同步。

//这将为所选引脚选择异步(无限定条件)。

//

GpioCtrlRegs.GPAQSEL2.bit.GPIO30 = 3; // GPIO30的异步量(CANRXA)

//GpioCtrlRegs.GPAQSEL2.bit.GPIO18 = 3; // GPIO18 (CANRXA)的异步定量