大家好,

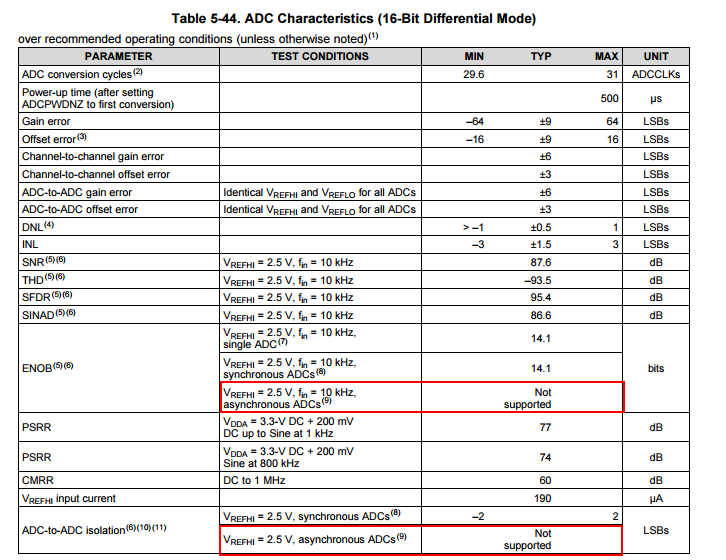

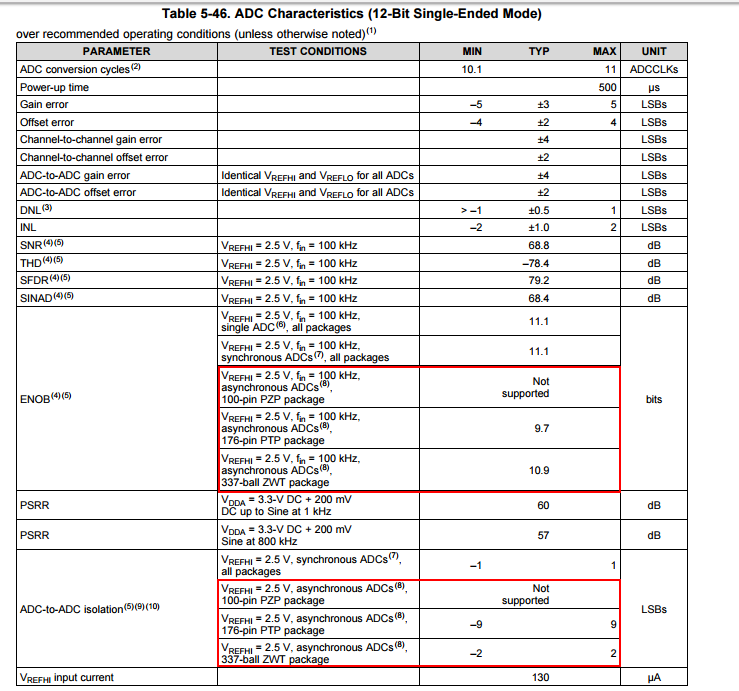

我们正在开发F2.8379万D Delfino part 337球栅。 要求是在16位模式下使用同步V/I对采样3相电压和电流。 我对Delfino中的4个ADC模块有点困惑,因此请确认此方案是否按预期工作。 所有SOC的触发源均为timer0。 SOC0应触发VA和IA模拟采样,SOC1 Vb,IB和SOC2 VC和IC。

差速器输入 模块 SOC

VA C2,C3 C 0

IA D0,D1 D 0

VB C4,C5 C 1

IB D2,D3 D 1.

VC B4,B5 B 2

IC D4,D5 D 2 <-最后一次转换

此外,在spruhm8f中提到SOCC和SOCD,这是否属于拼写错误?

提前感谢