我的整流器应用中使用了两对互补PWM,即EPWM1A/B和EPWM2A/B。 变量"CmdRun"用于控制 设置为1时运行的所有4个PWM,设置为0时停止。

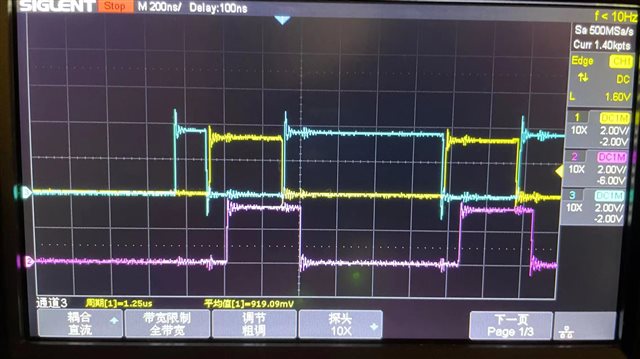

要求1:每次 CmdRun=1时,4个PWM的启动顺序都必须相同,与初始化配置中相同(EPWM1上升计数模式,EPWM1.TPRD=100,EPWM1.CMPA=10,EPWM1.MPPA =0, PRD设置为零,清除CPMA事件时为零;EPWAQ上升计数模式,EPWM2.CMB=20,EPWM2=CMB=100 EPWM2.TBCTR = 0,AQ设置在 CMPA上,清除CMBB事件,TBCLK=EPWMCLK=100MHz)。

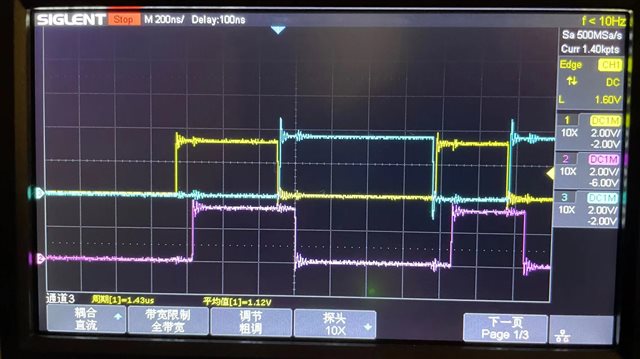

要求2:对于停止序列,当 CmdRun=0时 ,所有4个PWM应同时清除为低电平,没有10ns延迟。

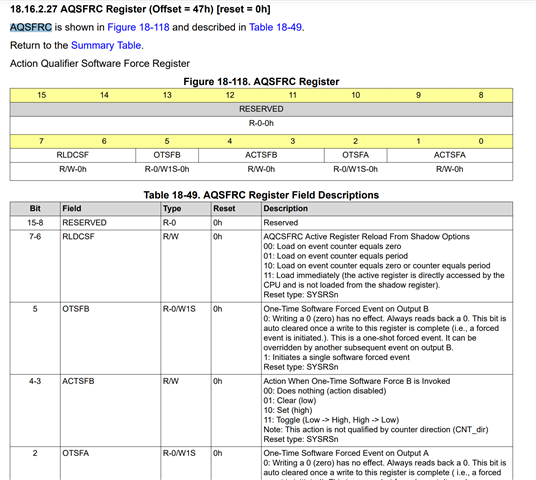

我当前的设计是通过软件使用一触式(OST)。 下面提供了一些代码。 但代码的连续执行似乎会导致一些操作延迟。 EPWM2将比EPWM1更早运行,因为它清除EPWM1之前的OST状态。 EPWM1将在EPWM2之前停止,因为它强制OST先于EPWM2。 你能否就如何实现上述要求给我一些建议?

IF (STaterun==0)

{

IF (CmdRun=1)

{

EPwm1Regs.TBCTL.bit.SWFSYNC = 1;//强制TBCTR重置。

EALLOW;

EPwm2Regs.TZCLr.bit.OST = 1;//清除单触发(OST)条件。

EPwm1Regs.TZCLr.bit.OST = 1;//清除单触发(OST)条件。

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;//所有ePWM时基时钟均以TBCLK的上升沿对齐启动。

EDIS;

Staterun = 1;

}

}

否则

{

如果(CmdRun=0)

{

EALLOW;

EPwm1Regs.TZFRC.bit.OST = 1;//通过软件强制单触发(OST)。 Q1先出。

EPwm2Regs.TZFRC.bit.OST = 1;//通过软件强制单触发(OST)。

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;//所有ePWM模块的时基时钟停止。

EDIS;

EPwm1Regs.TBCTL.bit.SWFSYNC = 1;//强制TBCTR重置。

Staterun = 0;

}

}