尊敬的团队:

我的客户使用 CMPSS 模块来检测 和比较 AD 端口电压。 检测有效后、TZ 信号被触发以关闭 PWM 输出。 他的设置如下:

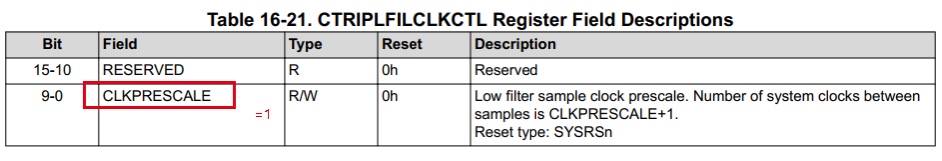

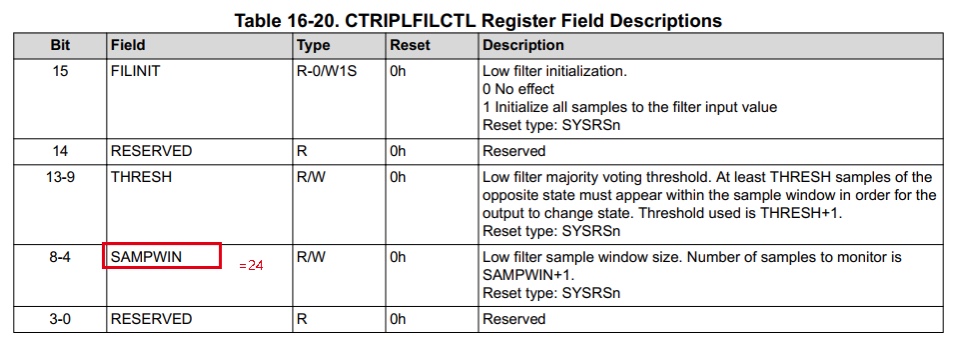

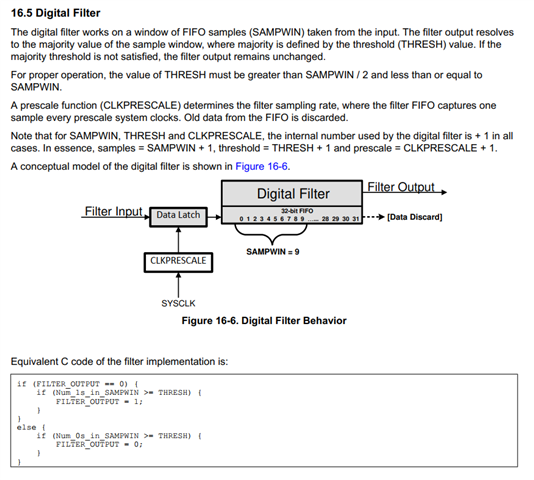

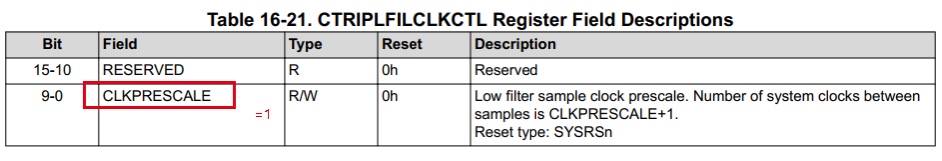

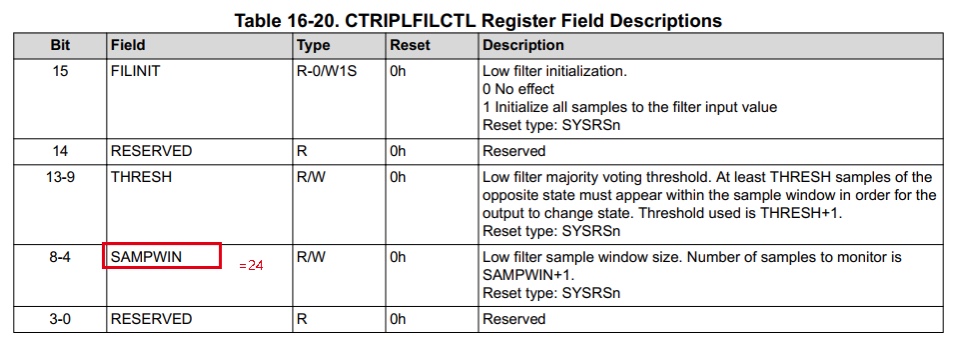

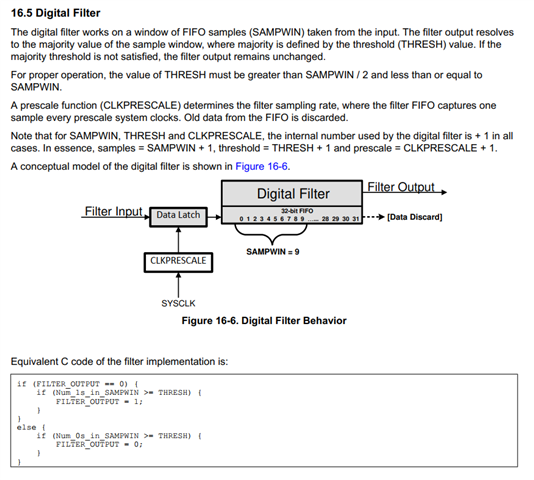

CLKPRESCALE = 2,SAMWIN = 25,SYSCLK = 100M。

在上述设置之后、理论保护触发时间是否为500ns?

但是、客户测量需要1.56us。 是设置问题还是计算问题?

此致、

绿色

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

我的客户使用 CMPSS 模块来检测 和比较 AD 端口电压。 检测有效后、TZ 信号被触发以关闭 PWM 输出。 他的设置如下:

CLKPRESCALE = 2,SAMWIN = 25,SYSCLK = 100M。

在上述设置之后、理论保护触发时间是否为500ns?

但是、客户测量需要1.56us。 是设置问题还是计算问题?

此致、

绿色

根据您的看法、我正在查看问题

这是我们的 cmpss--Xbar--PWM 的寄存器配置

#define CFG_BSP_CURR_CMPSS_FILTER_CLK_PRESCAL 1.

#define CFG_BSP_IU_CMPSS 高位 SAMPLEWINDOW 25.

//CMPSS1-input1

//选择 CMPHPM[object Object]SEL 的值。

ASysCtl_selectCMPHPMUX (ASYSCTL_CMPHPMUX_SELECT_1、CFG_BSP_IU_CMPSS INPUT_NUM);

//选择 CMPLPM[object Object]SEL 的值。

ASysCtl_selectCMPLPMUX (ASYSCTL_CMPLPMUX_SELECT_1、CFG_BSP_IU_CMPSS INPUT_NUM);

CMPSS_CONFIGHighComparator (CFG_BSP_IU_CMPSS_BASE、(CMPSS_INSRC_DAC));

//设置低电平比较器的配置。

CMPSS_CONFIGLowComparator (CFG_BSP_IU_CMPSS_BASE、(CMPSS_INSRC_DAC)| CMPSS_INV_IN倒 相);

//设置内部比较器 DAC 的配置。

CMPSS_CONFIGDAC (CFG_BSP_IU_CMPSS、(CMPSS_DACVAL_SYSCLK | CMPSS_DACREF_VDDA | CMPSS_DACSRC_Shdw);

//设置高比较器的内部 DAC 值。

CMPSS_setDACValueHigh (CFG_BSP_IU/CMPSS_BASE、2048 + CFG_BSP_IU/CMPSS_HIGH_VALUE);

//设置低比较器的内部 DAC 的值。

CMPSS_setDACValueLow (CFG_BSP_IU/CMPSS_BASE、2048 - CFG_BSP_IU/CMPSS_LOW_VALUE);

// 配置高比较器的数字滤波器。

CMPSS_CONFIGFILTERHigh (CFG_BSP_IU/CMPSS_BASE、CFG_BSP_CURR_CMPSS_FILTER_CLK_PRESCAL、CFG_BSP_IU/CMPSS_HIGH_SAMPLEWINDOW、(CFG_BSP_IU/CMPSS_HIGH_SAMPLEWINDOW / 2)+) 1U;

//配置低比较器的数字滤波器。

CMPSS 配置滤波器低电平(CFG_BSP_IU_CMPSS 基本输入、CFG_BSP_CURR_CMPSS 滤波器_CLK_PRESCAL、CFG_BSP_IU_CMPSS 低电平_SAMPLEWINDOW、(CFG_BSP_IU_CMPSS 低电平_SAMPLEWINDOW / 2)+);1U;

CMPSS_initFilterHigh (CFG_BSP_IU_CMPSS_BASE);

CMPSS_initFilterLow (CFG_BSP_IU_CMPSS_BASE);

CMPSS_CONFIGOutputsHigh (CFG_BSP_IU_CMPSS_BASE、(CMPSS_TRIPOUT_FILTER | CMPSS_TRIP_FILTER));

//设置低电平比较器的输出信号配置。

CMPSS_CONFIGOutputsLow (CFG_BSP_IU_CMPSS_BASE、(CMPSS_TRIPOUT_FILTER | CMPSS_TRIP_FILTER));

//设置比较器迟滞设置。

CMPSS_set迟滞(CFG_BSP_IU/CMPSS_BASE、1U);

CMPSS clearFilterLatchHigh (CFG_BSP_IU_CMPSS);

CMPSS clearFilterLatchLow (CFG_BSP_IU_CMPSS);

CMPSS_disableLatchResetOnPWMSYNCHigh (CFG_BSP_IU_CMPSS);

//禁用 PWMSYNC 上低比较器数字滤波器输出锁存的复位

CMPSS_disableLatchResetOnPWMSYNCLow (CFG_BSP_IU_CMPSS);

//设置保持复位跳闸的 EPWM 模块消隐信号。

CMPSS_CONFIG消 隐(CFG_BSP_IU/CMPSS_BASE、1U);

//禁用 ePWM 消隐信号,使跳闸保持在复位状态。

CMPSS_disableBlanking (CFG_BSP_IU_CMPSS_BASE);

//配置数字滤波器锁存器是否由 PWMSYNC 复位

CMPSS_CONFIGLatchOnPWMSYNC (CFG_BSP_IU_CMPSS_BASE、false、false);

Xbar_setEPWMMuxConfig (XBAR_TRIP4、XBAR_EPWM_MUX00_CMPSS1_CTRIPH_OR_L);

Xbar_enableEPWMMUX (XBAR_TRIP4、XBAR_MUX00);

Xbar_setEPWMMuxConfig (XBAR_TRIP5、XBAR_EPWM_MUX04_CMPSS3_CTRIPH_OR_L);

Xbar_enableEPWMMUX (XBAR_TRIP5、XBAR_MUX04);

Xbar_setEPWMMuxConfig (XBAR_TRIP7、XBAR_EPWM_MUX02_CMPSS2_CTRIPH_OR_L);

Xbar_enableEPWMMUX (XBAR_TRIP7、XBAR_MUX02);

Xbar_setEPWMMuxConfig (XBAR_TRIP8、XBAR_EPWM_MUX06_CMPSS4_CTRIPH_OR_L);

Xbar_enableEPWMMUX (XBAR_TRIP8、XBAR_MUX06);

ePWM_setTripZoneAction (EPWM1_base、ePWM_TZ_ACT_EVENT_TZA、

ePWM_TZ_ACT_HIGH_Z);

// DCAH 为高电平时触发事件

//

ePWM_setTripZoneDigitalCompareEventCondition (EPWM1_BASE、

ePWM_TZ_DC_OUTPUT _A1、

ePWM_TZ_EVENT_DCXH_HIGH);

//

//将 DCAH 配置为使用 TRIP4 或 TRIP5作为输入

//

ePWM_enableDigitalCompareTripCombinationInput (EPWM1_base、

(ePWM_DC_combinational_TRIPIN4 | ePWM_DC_combinational_TRIPIN5

|ePWM_DC_combinational_TRIPIN7 | ePWM_DC_combinational_TRIPIN8)、

ePWM_DC_TYPE_DCAH);

//将 DCA 启用为 OST

//

ePWM_enableTripZoneSignals (EPWM1_base、ePWM_TZ_SIGNEL_DCAEVT1);

//

//将 DCA 路径配置为未过滤和异步

//

ePWM_setDigitalCompareEventSource (EPWM1_BASE、

ePWM_DC_MODULE_A、

ePWM_DC_EVENT_1、

ePWM_DC_EVENT_SOURC_ORIG_SIGNAL);

ePWM_setDigitalCompareEventSyncMode (EPWM1_BASE、

ePWM_DC_MODULE_A、

ePWM_DC_EVENT_1、

ePWM_DC_EVENT_INPUT_NOT 已同步);

您好 Matthew:

客户表示做过、但感觉不好。 这是它们的 cmpss--Xbar--PWM 配置:

1、CMPSS 配置:

#define CFG_BSP_CURR_CMPSS_FILTER_CLK_PRESCAL 1

#define CFG_BSP_IU_CMPSS_HIGH_SAMPLEWINDOW 25

//CMPSS1-input1

// Select the value for CMPHPM[object Object]SEL.

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_1,CFG_BSP_IU_CMPSS_INPUT_NUM);

// Select the value for CMPLPM[object Object]SEL.

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_1,CFG_BSP_IU_CMPSS_INPUT_NUM);

CMPSS_configHighComparator(CFG_BSP_IU_CMPSS_BASE,(CMPSS_INSRC_DAC));

// Sets the configuration for the Low comparator.

CMPSS_configLowComparator(CFG_BSP_IU_CMPSS_BASE,(CMPSS_INSRC_DAC)| CMPSS_INV_INVERTED);

// Sets the configuration for the internal comparator DACs.

CMPSS_configDAC(CFG_BSP_IU_CMPSS_BASE,(CMPSS_DACVAL_SYSCLK | CMPSS_DACREF_VDDA | CMPSS_DACSRC_SHDW));

// Sets the value of the internal DAC of the high comparator.

CMPSS_setDACValueHigh(CFG_BSP_IU_CMPSS_BASE,2048 + CFG_BSP_IU_CMPSS_HIGH_VALUE);

// Sets the value of the internal DAC of the low comparator.

CMPSS_setDACValueLow(CFG_BSP_IU_CMPSS_BASE, 2048 - CFG_BSP_IU_CMPSS_LOW_VALUE);

// Configures the digital filter of the high comparator.

CMPSS_configFilterHigh(CFG_BSP_IU_CMPSS_BASE, CFG_BSP_CURR_CMPSS_FILTER_CLK_PRESCAL, CFG_BSP_IU_CMPSS_HIGH_SAMPLEWINDOW, (CFG_BSP_IU_CMPSS_HIGH_SAMPLEWINDOW / 2) + 1u);

// Configures the digital filter of the low comparator.

CMPSS_configFilterLow(CFG_BSP_IU_CMPSS_BASE, CFG_BSP_CURR_CMPSS_FILTER_CLK_PRESCAL, CFG_BSP_IU_CMPSS_LOW_SAMPLEWINDOW, (CFG_BSP_IU_CMPSS_LOW_SAMPLEWINDOW / 2) + 1u);

CMPSS_initFilterHigh(CFG_BSP_IU_CMPSS_BASE);

CMPSS_initFilterLow(CFG_BSP_IU_CMPSS_BASE);

CMPSS_configOutputsHigh(CFG_BSP_IU_CMPSS_BASE,(CMPSS_TRIPOUT_FILTER | CMPSS_TRIP_FILTER));

// Sets the output signal configuration for the low comparator.

CMPSS_configOutputsLow(CFG_BSP_IU_CMPSS_BASE, (CMPSS_TRIPOUT_FILTER | CMPSS_TRIP_FILTER));

// Sets the comparator hysteresis settings.

CMPSS_setHysteresis(CFG_BSP_IU_CMPSS_BASE,1U);

CMPSS_clearFilterLatchHigh(CFG_BSP_IU_CMPSS_BASE);

CMPSS_clearFilterLatchLow(CFG_BSP_IU_CMPSS_BASE);

CMPSS_disableLatchResetOnPWMSYNCHigh(CFG_BSP_IU_CMPSS_BASE);

// Disables reset of LOW comparator digital filter output latch on PWMSYNC

CMPSS_disableLatchResetOnPWMSYNCLow(CFG_BSP_IU_CMPSS_BASE);

// Sets the ePWM module blanking signal that holds trip in reset.

CMPSS_configBlanking(CFG_BSP_IU_CMPSS_BASE,1U);

// Disables an ePWM blanking signal from holding trip in reset.

CMPSS_disableBlanking(CFG_BSP_IU_CMPSS_BASE);

// Configures whether or not the digital filter latches are reset by PWMSYNC

CMPSS_configLatchOnPWMSYNC(CFG_BSP_IU_CMPSS_BASE,false,false);

2、 XBAR 配置

XBAR_setEPWMMuxConfig(XBAR_TRIP4, XBAR_EPWM_MUX00_CMPSS1_CTRIPH_OR_L);

XBAR_enableEPWMMux(XBAR_TRIP4, XBAR_MUX00);

XBAR_setEPWMMuxConfig(XBAR_TRIP5, XBAR_EPWM_MUX04_CMPSS3_CTRIPH_OR_L);

XBAR_enableEPWMMux(XBAR_TRIP5, XBAR_MUX04);

XBAR_setEPWMMuxConfig(XBAR_TRIP7, XBAR_EPWM_MUX02_CMPSS2_CTRIPH_OR_L);

XBAR_enableEPWMMux(XBAR_TRIP7, XBAR_MUX02);

XBAR_setEPWMMuxConfig(XBAR_TRIP8, XBAR_EPWM_MUX06_CMPSS4_CTRIPH_OR_L);

XBAR_enableEPWMMux(XBAR_TRIP8, XBAR_MUX06);

3、 ePWM 配置

EPWM_setTripZoneAction(EPWM1_BASE, EPWM_TZ_ACTION_EVENT_TZA,

EPWM_TZ_ACTION_HIGH_Z);

// Trigger event when DCAH is high

//

EPWM_setTripZoneDigitalCompareEventCondition(EPWM1_BASE,

EPWM_TZ_DC_OUTPUT_A1,

EPWM_TZ_EVENT_DCXH_HIGH);

//

// Configure DCAH to use TRIP4 OR TRIP5 as an input

//

EPWM_enableDigitalCompareTripCombinationInput(EPWM1_BASE,

(EPWM_DC_COMBINATIONAL_TRIPIN4 | EPWM_DC_COMBINATIONAL_TRIPIN5

|EPWM_DC_COMBINATIONAL_TRIPIN7 | EPWM_DC_COMBINATIONAL_TRIPIN8),

EPWM_DC_TYPE_DCAH);

// Enable DCA as OST

//

EPWM_enableTripZoneSignals(EPWM1_BASE, EPWM_TZ_SIGNAL_DCAEVT1);

//

// Configure the DCA path to be unfiltered and asynchronous

//

EPWM_setDigitalCompareEventSource(EPWM1_BASE,

EPWM_DC_MODULE_A,

EPWM_DC_EVENT_1,

EPWM_DC_EVENT_SOURCE_ORIG_SIGNAL);

EPWM_setDigitalCompareEventSyncMode(EPWM1_BASE,

EPWM_DC_MODULE_A,

EPWM_DC_EVENT_1,

EPWM_DC_EVENT_INPUT_NOT_SYNCED);

此致、

绿色

Tony、

我认为这篇文章和 TI 员工的另一篇文章涉及同一个问题。 您能告诉我这是否相同、我将合并线程吗?

最棒的

Matthew