主题中讨论的其他器件:C2000WARE

您好、专家、

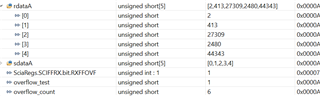

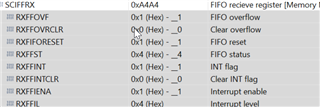

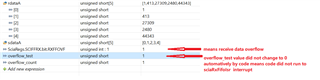

我的客户遇到 SCI 接收溢出和 SciaRegs.SCIFFRX.bit.RXFFOVF 为1的问题、但有时未进入中断。

正如 TRM 提到的、 当 SCI 接收溢出发生时、应该能够进入中断。

我使用控制卡进行了测试、并按照如下方式修改了 c2000ware 中的代码、当 在 CCS 窗口中设置 overflow_test=1时、将不会读取数据并导致接收数据溢出:

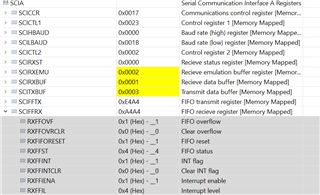

在 sciaRxFifoIsr 中、还根据标志 SciaRegs.SCIFFRX.bit.RXFFOVF 复位 SCI。

sciaRxFifoIsr(void)

{

Uint16 i;

if(SciaRegs.SCIFFRX.bit.RXFFOVF ==1)

{

overflow_test = 0;

SciaRegs.SCICTL1.all = 0x0023;

SciaRegs.SCIFFTX.bit.TXFIFOXRESET = 1;

SciaRegs.SCIFFRX.bit.RXFIFORESET = 1;

overflow_count++;

}

if(overflow_test ==0)

{

for(i=0;i<1;i++)

rdataA[i]=SciaRegs.SCIRXBUF.all; // Read data

}

只需将 overflow_test 设置为1并查看结果、执行多次测试即可发现 、SciaRegs.SCIFFRX.bit.RXFFOVF 为1、但未 再次进入中断 sciaRxFifoIsr。

这里有什么问题吗? 为什么 会出现 SciaRegs.SCIFFRX.bit.RXFFOVF 为1但代码没有运行到 sciaRxFifoIsr 的情况 ?