主题中讨论的其他器件:UNIFLASH、 C2000WARE

我正在尝试使用 TI 的 UNIFLASH 8.0来刷写 F28388D 卡(MCU063B)。 但它的剂量不起作用。 以下是错误消息:

该程序是从 TI 网站"led_ex1_blinky.txt"下载的简单程序。

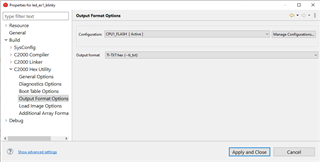

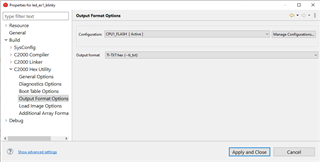

输出格式设置为:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我正在尝试使用 TI 的 UNIFLASH 8.0来刷写 F28388D 卡(MCU063B)。 但它的剂量不起作用。 以下是错误消息:

该程序是从 TI 网站"led_ex1_blinky.txt"下载的简单程序。

输出格式设置为:

您好 Vamsi;

我没有修改链接命令文件中的任何内容。 我刚才下载了整个项目"led_ex1_blinky"并运行它。 我可以在 CCS 中的 RAM 中成功运行它、并且可以在 CCS 中成功运行它并以闪存模式对其进行编程。 我无法使用 UniFlash 对其进行编程。

我从 C2000ware - 4.01.00.00下的示例中下载了该软件:F2838x => c28=>led_ex1_blinky。

我将输出文件格式设置为 TI-TXT。

这是一个非常简单的程序。 您能否验证您是否可以使用侧面的"UniFlash"对其进行编程。

为了方便、我粘贴了下面的链接命令文件。 同样、我没有修改任何内容、它与"Resource Explorer"中的示例完全相同

===========================

存储器

{

/* begin 用于"引导至闪存"引导加载程序模式*/

开始:origin = 0x080000,length = 0x000002

BOOT_RSVD:origin = 0x000002,length = 0x0001AF // M0的部分,引导 ROM 将此用于栈*/

RAMM0:origin = 0x0001B1,length = 0x00024F

RAMM1:origin = 0x000400,length = 0x0003F8 //片上 RAM 块 M1 */

// RAMM1_RSVD:origin = 0x0007F8,length = 0x000008 //根据勘误咨询“Memory:Prepetching Beyond valid Memory”(内存:超出有效内存的预取),保留并不用于代码*/

RAMD0:origin = 0x00C000、length = 0x000800

RAMD1:origin = 0x00C800,length = 0x000800

RAMLS0:origin = 0x008000、length = 0x000800

RAMLS1:origin = 0x008800,length = 0x000800

RAMLS2:origin = 0x009000,length = 0x000800

RAMLS3:origin = 0x009800,length = 0x000800

RAMLS4:origin = 0x00A000,length = 0x000800

RAMLS5:origin = 0x00A800,length = 0x000800

RAMLS6:origin = 0x00B000、length = 0x000800

RAMLS7:origin = 0x00B800,length = 0x000800

RAMGS0:origin = 0x00D000,length = 0x001000

RAMGS1:origin = 0x00E000、length = 0x001000

RAMGS2:origin = 0x00F000、length = 0x001000

RAMGS3:origin = 0x010000,length = 0x001000

RAMGS4:origin = 0x011000,length = 0x001000

RAMGS5:origin = 0x012000,length = 0x001000

RAMGS6:origin = 0x013000、length = 0x001000

RAMGS7:origin = 0x014000,length = 0x001000

RAMGS8:origin = 0x015000,length = 0x001000

RAMGS9:origin = 0x016000,length = 0x001000

RAMGS10:origin = 0x017000,length = 0x001000

RAMGS11:origin = 0x018000,length = 0x001000

RAMGS12:origin = 0x019000,length = 0x001000

RAMGS13:origin = 0x01A000,length = 0x001000

RAMGS14:origin = 0x01B000,length = 0x001000

RAMGS15:origin = 0x01C000,length = 0x000FF8

// RAMGS15_RSVD:origin = 0x01CFF8,length = 0x000008 //根据勘误咨询“Memory: pret撷取 超出有效内存”*/,保留并不用于代码

/*闪存扇区*/

FLASH0:origin = 0x080002,length = 0x001FFE /*片上闪存*/

FLASH1:origin = 0x082000,length = 0x002000 //片上闪存*/

FLASH2:origin = 0x084000、length = 0x002000 //片上闪存*/

FLASH3:origin = 0x086000、length = 0x002000 //片上闪存*/

FLASH4:origin = 0x088000、length = 0x008000 //片上闪存*/

FLASH5:origin = 0x090000,length = 0x008000 //片上闪存*/

Flash6:origin = 0x098000、length = 0x008000 //片上闪存*

FLASH7:origin = 0x0A0000,length = 0x008000 //片上闪存*/

FLASH8:origin = 0x0A8000、length = 0x008000 //片上闪存*/

FLASH9:origin = 0x0B0000,length = 0x008000 //片上闪存*/

FLASH10:origin = 0x0B8000、length = 0x002000 //片上闪存*/

FLASH11:origin = 0x0BA000、length = 0x002000 //片上闪存*/

FLASH12:origin = 0x0BC000、length = 0x002000 //片上闪存*/

FLASH13:origin = 0x0BE000、length = 0x001FF0 /*片上闪存*/

// FLASH13_RSVD:origin = 0x0BFFF0,length = 0x000010 //根据勘误咨询“Memory:Prepetching Beyond valid Memory”(内存:有效内存之外的预取)来保留代码,不要将其用于代码*/

CPU1TOCPU2RAM:origin = 0x03A000,length = 0x000800

CPU2TOCPU1RAM:origin = 0x03B000,length = 0x000800

CPUTOCMRAM:origin = 0x039000,length = 0x000800

CMTOCPURAM:origin = 0x038000,length = 0x000800

CANA_MSG_RAM:origin = 0x049000、length = 0x000800

CANB_MSG_RAM:origin = 0x04B000、length = 0x000800

复位:origin = 0x3FFFC0,length = 0x000002

}

部分

{

codestart:>开始,align (8)

.text:>> FLASH1 | FLASH2 | FLASH3 | FLASH4、ALIGN (8)

.cinit:> FLASH4,align (8)

.switch:> FLASH1,ALIGN(8)

.reset:> reset,type = DSECT /* not used,*/

.stack:> RAMM1

#if defined (_TI_EABI)

init_array:> FLASH1,align (8)

.bss:> RAMLS5

.bss:输出:> RAMLS3

.bss:CIO :>RAMLS5

.data :> RAMLS5

.sysmem:> RAMLS5

/*初始化段进入闪存*/

.const:> FLASH5、align (8)

其他

.pinit:> FLASH1,align (8)

.ebss:> RAMLS5

.esysmem:> RAMLS5

.cio:> RAMLS5

/*初始化段进入闪存*/

.econst:>> FLASH4 | FLASH5、ALIG(8)

#endif

ramgs0:>RAMGS0,type=NOINIT

ramgs1:>RAMGS1,type=NOINIT

MSGRAM_CPU1_TO_CPU2:>CPU1TOCPU2RAM,type=NOINIT

MSGRAM_CPU2_TO_CPU1:>CPU2TOCPU1RAM,type=NOINIT

MSGRAM_CPU_TO_CM:> CPUTOCMRAM,type=NOINIT

MSGRAM_CM_TO_CPU:> CMTOCPURAM,type=NOINIT

/*以下部分定义适用于 SDFM 示例*/

filter_RegsFile:> RAMGS0

filter1_RegsFile:> RAMGS1,fill=0x1111

Filter2_RegsFile:> RAMGS2,fill=0x2222

Filter3_RegsFile:> RAMGS3,fill=0x3333

Filter4_RegsFile:> RAMGS4,fill=0x4444

Differit_RegsFile:>RAMGS5,fill=0x3333

#if defined (_TI_EABI)

.TI.ramfunc:{}负载= FLASH3,

RUN = RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3、

Load_start (RamfuncsLoadStart)、

load_size (RamfuncsLoadSize)、

Load_End (RamfuncsLoadEnd)、

RUN_START (RamfuncsRunStart)、

run_size (RamfuncsRunSize)、

RUN_END (RamfuncsRunEnd)、

对齐(8)

其他

.TI.ramfunc:{}负载= FLASH3,

RUN = RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3、

load_start (_RamfuncsLoadStart)、

load_size (_RamfuncsLoadSize)、

load_end (_RamfuncsLoadEnd)、

run_start (_RamfuncsRunStart)、

run_size (_RamfuncsRunSize)、

run_end (_RamfuncsRunEnd)、

对齐(8)

#endif

}

/*

//============================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================

//文件结束。

//============================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================================

*