主题中讨论的其他器件:C2000WARE

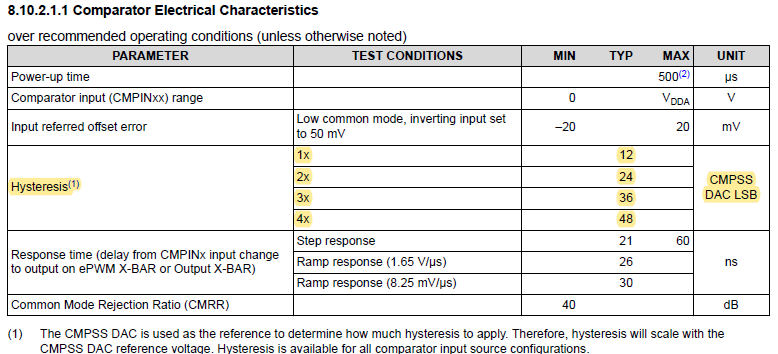

大家好、我在系统中遇到了使用 ADC 测量的高噪声交流信号、以及通过比较器和 ECAP 模块计算的周期。 无噪声信号的计算很好(到小数位数的2)、但噪声信号的计算很差。 我知道噪声触发比较器和 ECAP 只是测量这种上升沿、但是否有任何用于降低比较器噪声的解决方案、例如采用迟滞的降噪或软件施密特触发解决方案? 是否有人对最合适的方法有任何经验?

示例1:如果我在 ADC 输入端有高谐波交流信号(例如、30-40谐波10%)、我得到计算周期错误(例如50Hz 交流信号时为0.25ms、应为20ms)

示例2:50Hz ECAP 时的纯交流信号测量非常好、如50.002Hz

我已将 cmpss 滤波器放大:

Cmpss6Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE = 90;

Cmpss6Regs.CTRIPHFILCTL.bit.SAMPWIN = 0x1F;

Cmpss6Regs.CTRIPHFILCTL.bit.THRESH = 0x1F;

Cmpss6Regs.CTRIPHFILCTL.bit.FILINIT = 1;

使用具有比较器6的 ADC-C 输入2的 IM 从输入 x 条7进入 eCAP1。 周期在 eCAP1中断中计算。

使用手动重新布防进行 ECAP 设置。

ECap1Regs.ECCTL2.bit.TSCTRSTOP = 0; // Stop the TSCTR counter

ECap1Regs.ECEINT.all = 0; // Disable eCAP1 interrupts

ECap1Regs.ECCLR.all = 0x00FF; // Clear eCAP1 interrupt flags

ECap1Regs.CTRPHS = 0;

ECap1Regs.ECCTL2.bit.CAP_APWM = 0; // ECAP module operates in capture mode

ECap1Regs.ECCTL2.bit.SYNCI_EN = 0; // disable counter (TSCTR) to be loaded from CTRPHS

ECap1Regs.ECCTL2.bit.SWSYNC = 1;

ECap1Regs.ECCTL2.bit.STOP_WRAP = 2; // for continuous mode wrap value 2; wrap after Capture Event 3

ECap1Regs.ECCTL2.bit.SYNCO_SEL = 0; // Select sync-in event to be the sync-out signal (pass through)

ECap1Regs.ECCTL2.bit.CONT_ONESHT = 1; // Operate in One-Shot mode

//ECap1Regs.ECCTL2.bit.CONT_ONESHT = 0; // Operate in Continuos mode

ECap1Regs.ECCTL1.bit.PRESCALE = 0; // Divide by 1 (i.e,. no prescale, by-pass the event prescaler)

ECap1Regs.ECCTL1.bit.CAPLDEN = 1; // Enable CAP1-4 register loads at capture event time.

ECap1Regs.ECCTL1.bit.CAP1POL = 0; // Capture Event 1 triggered on a rising edge (RE)

ECap1Regs.ECCTL1.bit.CAP2POL = 0; // Capture Event 2 triggered on a rising edge (RE)

ECap1Regs.ECCTL1.bit.CAP3POL = 0; // Capture Event 3 triggered on a rising edge (RE)

ECap1Regs.ECCTL1.bit.CAP4POL = 0; // Capture Event 4 triggered on a rising edge (RE)

ECap1Regs.ECCTL1.bit.CTRRST1 = 0; // Reset counter after Capture Event 1 time-stamp has been captured

ECap1Regs.ECCTL1.bit.CTRRST2 = 0; // Do not reset counter on Capture Event 2

ECap1Regs.ECCTL1.bit.CTRRST3 = 0; // Do not reset counter on Capture Event 3

ECap1Regs.ECCTL1.bit.CTRRST4 = 0; // Do not reset counter on Capture Event 4

//ECap1Regs.ECEINT.bit.CEVT3 = 1; // CEVT3 Interrupt enable

//ECap1Regs.ECEINT.bit.CTROVF = 1; // CTROVF Interrupt enable

ECap1Regs.ECCTL2.bit.SYNCI_EN = 0; // disable counter (TSCTR) to be loaded from CTRPHS

谢谢。

-Marek。